#### LIMITED WARRANTY

#### I. CUSTOMER OBLIGATIONS

- A. CUSTOMER assumes full responsibility that this computer hardware purchased (the "Equipment"), and any copies of software included with the Equipment or licensed separately (the "Software") meets the specifications, capacity, capabilities, versatility, and other requirements of CUSTOMER.

- B. CUSTOMER assumes full responsibility for the condition and effectiveness of the operating environment in which the Equipment and Software are to function, and for its installation.

#### II. LIMITED WARRANTIES AND CONDITIONS OF SALE

- A. For a period of ninety (90) calendar days from the date of the Radio Shack sales document received upon purchase of the Equipment. RADIO SHACK warrants to the original CUSTOMER that the Equipment and the medium upon which the Software is stored is free from manufacturing delects. This warranty is only applicable to purchases of Tandy Equipment by the original customer from Radio Shack company-owned computer centers, retail stores, and Radio Shack franchisees and dealers at their authorized locations. The warranty is void if the Equipment or Software has been subjected to improper or abnormal use. If a manufacturing defect is discovered during the stated warranty period, the defective Equipment must be returned to a Radio Shack Computer Center, a Radio Shack retail store, a participating Radio Shack franchisee or a participating Radio Shack dealer for repair, along with a copy of the sales document or lease agreement. The original CUSTOMER'S sole and exclusive remedy in the event of a defect is limited to the correction of the defect by repair, replacement, or refund of the purchase price, at RADIO SHACK'S election and sole expense. RADIO SHACK has no obligation to replace or repair expendable items.

- B. RÁDIO SHAČK makes no warranty as to the design, capability, capacity, or suitability for use of the Software, except as provided in this paragraph. Software is licensed on an "AS IS" basis, without warranty. The original CUSTOMER'S exclusive remedy, in the event of a Software manufacturing defect, is its repair or replacement within thirty (30) calendar days of the date of the Radio Shack sales document received upon license of the Software. The defective Software shall be returned to a Radio Shack Computer Center, a Radio Shack retail store, a participating Radio Shack franchisee or Radio Shack dealer along with the sales document.

- Except as provided herein no employee, agent, franchisee, dealer or other person is authorized to give any warranties of any nature on behalf of RADIO SHACK.

- EXCEPT AS PROVIDED HEREIN, RADIO SHACK MAKES NO EXPRESS WARRANTIES, AND ANY IMPLIED WARRANTY OF MERCHANTABILITY OR

FITNESS FOR A PARTICULAR PURPOSE IS LIMITED IN ITS DURATION TO THE DURATION OF THE WRITTEN LIMITED WARRANTIES SET FORTH

HEREIN

- E. Some states do not allow limitations on how long an implied warranty lasts, so the above limitation(s) may not apply to CUSTOMER.

#### III. LIMITATION OF LIABILITY

- A. EXCEPT AS PROVIDED HEREIN, RADIO SHACK SHALL HAVE NO LIABILITY OR RESPONSIBILITY TO CUSTOMER OR ANY OTHER PERSON OR ENTITY WITH RESPECT TO ANY LIABILITY, LOSS OR DAMAGE CAUSED OR ALLEGED TO BE CAUSED DIRECTLY OR INDIRECTLY BY "EQUIPMENT" OR "SOFTWARE." SLOLD, LEASED, LICENSED OR FURNISHED BY RADIO SHACK, INCLUDING, BUT NOT LIMITED TO, ANY INTERRUPTION OF SERVICE, LOSS OF BUSINESS OR ANTICIPATORY PROFITS OR CONSEQUENTIAL DAMAGES RESULTING FROM THE USE OR OPERATION OF THE "EQUIPMENT" OR "SOFTWARE." IN NO EVENT SHALL RADIO SHACK BE LIABLE FOR LOSS OF PROFITS, OR ANY INDIRECT, SPECIAL, OR CONSEQUENTIAL DAMAGES ARISING OUT OF ANY BREACH OF THIS WARRANTY OR IN ANY MANNER ARISING OUT OF OR CONNECTED WITH THE SALE, LEASE, LICENSE, USE OR ANTICIPATED USE OF THE "EQUIPMENT" OR "SOFTWARE."

- NOTWITHSTANDING THE ABOVE LIMITATIONS AND WARRANTIES, RADIO SHACK'S LIABILITY HEREUNDER FOR DAMAGES INCURRED BY CUSTOMER OR OTHERS SHALL NOT EXCEED THE AMOUNT PAID BY CUSTOMER FOR THE PARTICULAR "EQUIPMENT" OR "SOFTWARE" INVOLVED.

- B. RADIO SHACK shall not be liable for any damages caused by delay in delivering or furnishing Equipment and/or Software.

- C. No action arising out of any claimed breach of this Warranty or transactions under this Warranty may be brought more than two (2) years after the cause of action has accrued or more than four (4) years after the date of the Radio Shack sales document for the Equipment or Software, whichever first occurs.

- D. Some states do not allow the limitation or exclusion of incidental or consequential damages, so the above limitation(s) or exclusion(s) may not apply to CUSTOMER.

#### IV. SOFTWARE LICENSE

RADIO SHACK grants to CUSTOMER a non-exclusive, paid-up license to use the TANDY Software on one computer, subject to the following provisions:

- A. Except as otherwise provided in this Software License, applicable copyright laws shall apply to the Software.

- B. Title to the medium on which the Software is recorded (cassette and/or diskette) or stored (ROM) is transferred to CUSTOMER, but not title to the Software.

- C. CUSTOMER may use Software on a multiuser or network system only if either, the Software is expressly labeled to be for use on a multiuser or network system, or one copy of this software is purchased for each node or terminal on which Software is to be used simultaneously.

- D. CUSTOMER shall not use, make, manufacture, or reproduce copies of Software except for use on one computer and as is specifically provided in this Software License. Customer is expressly prohibited from disassembling the Software.

- CUSTOMER is permitted to make additional copies of the Software only for backup or archival purposes or if additional copies are required in the operation of one computer with the Software, but only to the extent the Software allows a backup copy to be made. However, for TRSDOS Software, CUSTOMER is permitted to make a limited number of additional copies for CUSTOMER'S own use.

- F. CUSTOMER may resell or distribute unmodified copies of the Software provided CUSTOMER has purchased one copy of the Software for each one sold or distributed. The provisions of this Software License shall also be applicable to third parties receiving copies of the Software from CUSTOMER.

- G. All copyright notices shall be retained on all copies of the Software.

#### V. APPLICABILITY OF WARRANTY

- A. The terms and conditions of this Warranty are applicable as between RADIO SHACK and CUSTOMER to either a sale of the Equipment and/or Software License to CUSTOMER or to a transaction whereby Radio Shack sells or conveys such Equipment to a third party for lease to CUSTOMER.

- B. The limitations of liability and Warranty provisions herein shall inure to the benefit of RADIO SHACK, the author, owner and or licensor of the Software and any manufacturer of the Equipment sold by Radio Shack.

#### VI. STATE LAW RIGHTS

The warranties granted herein give the original CUSTOMER specific legal rights, and the original CUSTOMER may have other rights which vary from state to state.

# Debug/Assembler

Model 100 Debug/Assembler Software: Copyright 1984, Microsoft. All Rights Reserved. Licensed to Tandy Corporation.

Model 100 Debug/Assembler Manual: Copyright 1984. Tandy Corporation. All Rights Reserved.

Reference section G/8085 Instruction Set and Reference section H/8085 Hardware Characteristics are reprinted by permission of Intel Corporation, Copyright 1984.

Reproduction or use without express written permission from Tandy Corporation, of any portion of this manual is prohibited. While reasonable efforts have been taken in the preparation of this manual to assure its accuracy, Tandy Corporation assumes no liability resulting from any errors or omissions in this manual, or from the use of the information contained herein.

# Contents

| Part I/ Getting Started3                          |

|---------------------------------------------------|

| Chapter 1/ Loading the Model 100 Debug/Assembler4 |

| Chapter 2/ Running a Sample Program               |

| Chapter 3/ Overview11                             |

| Part II/ Commands17                               |

| Chapter 4/ Examining Memory                       |

| (ZBUG Commands — Part I)18                        |

| Chapter 5/ Assembling the Program                 |

| (Assembler Commands)25                            |

| Chapter 6/ Debugging the Program                  |

| (ZBUG Commands — Part II)31                       |

| Chapter 7/ Using the ZBUG Calculator              |

| (ZBUG Commands — Part III)40                      |

| Part III/ Assembly Language49                     |

| Chapter 8/ Writing the Program50                  |

| Chapter 9/ Using Pseudo Ops58                     |

| Part IV/ ROM Routines63                           |

| Chapter 10/ Using the Keyboard and Video Display  |

| (ROM Routines)64                                  |

| Part V/ Reference67                               |

| A/ Assembler Commands and Switches                |

| B/ ZBUG Commands69                                |

| C/ ZBUG/Assembler Error Messages74                |

| D/ Assembler Pseudo Ops77                         |

| E/ ROM Subroutines                                |

| F/ ASCII Codes9                                   |

| G/ 8085 Instruction Set                           |

| H/ 8085 Hardware Characteristics                  |

| adou 140                                          |

#### To Our Customers ...

The heart of the Model 100 is an 8085 "processor." It controls all parts of the Model 100.

The processor understands only 0s and 1s, a code not at all intelligible to the human mind. This code is called "8085 machine code."

When you run a BASIC program, a system calls the "BASIC Interpreter" and translates each statement, one at a time, into 8085 machine code. This is an easy, but inefficient, way to program.

The Model 100 Debug/Assembler lets you program using an intelligible representation of 8085 machine code, called "assembly language," that talks directly to the processor. You then assemble the entire program into 8085 machine code before running it.

Programming with the Model 100 Debug/Assembler gives you these benefits:

- You have direct and complete control of the Model 100.

- You can use its many features—such as the assembler, disassembler, and breakpoint debugger—for memory location modification.

- Your program executes faster. This is because it is already translated into 8085 machine code when you run it.

Note: The page numbers referenced in the appendices refer to the Intel publication, The MSC® -80/85 Family User's Manual.

# To Use the Model 100 Debug/Assembler You Need...

A Model 100 Portable Computer with 32K of RAM, a cassette recorder, and the Model 100 Debug/Assembler program cassette tape.

#### This manual uses these terms and notations:

**KEY** A key you must press.

Italics A value you must supply.

filename A Model 100 file specification.

CAS: filename.ext

filename has 1-6 characters.

extension has 1-3 characters. If you omit the extension, the Model 100 Debug/Assembler uses .DO.

CAS: saves the file to cassette.

Η

A hexadecimal (Base 16) number. For example, OFH represents hexadecimal OF, which is equal to 15 in decimal (Base 10) notation. Hexadecimal numbers should always begin with a numeral so that the Model 100 Debug/Assembler can distinguish between the number and its corresponding register name. Use a leading O with hexadecimal numbers beginning with an A, B, C, D, E, or F.

# PART I/ GETTING STARTED

This section gets you started with the Model 100 Debug/Assembler and explains some concepts you need to know.

## CHAPTER 1/ LOADING THE MODEL 100 DEBUG/ASSEMBLER

This chapter shows how to load the Model 100 Debug/Assembler from cassette tape into your Model 100 memory and save it to RAM.

# Load the Model 100 Debug/Assembler From Cassette

Be sure your Model 100 is turned on and the cassette recorder properly connected. Insert the Model 100 Debug/Assembler cassette tape into the recorder and press the Play button.

Next, position the cursor over BASIC and press **ENTER**. At BASIC's OK prompt, type (in either uppercase or lowercase letters):

SOUND OFF (ENTER)

**Note:** Always be sure to turn off the Model 100's sound whenever you use the cassette recorder.

When the OK prompt appears, type:

CLEAR 0,49151 (ENTER)

Another OK prompt appears. Now type:

CLOADM ENTER

This procedure turns the sound off before loading the program, clears memory for the program, and then loads the program from the cassette.

**Note:** The Model 100 Debug/Assembler program is stored with the filename **ZBGASM**. The program-debugging portion of the Debug/Assembler is called ZBUG.

The computer shows that it has located the ZBGASM program by displaying:

Found: ZBGASM Top: 54272 End: 62475 Exe: 54275

The OK prompt signals that the Model 100 Debug/Assembler is in memory.

At this point you can either execute the program or save the program to RAM for future use.

To execute the program, type:

CALL 54272 ENTER

The screen shows the startup message and the ZBUG prompt:

M100 ZBGASM/01.xx.xx Copr. 1984 Microsoft

#

To save the program to RAM, type:

SAVEM "ZBGASM",54272,62475,54272 (ENTER)

Now press **F8** to return to the main menu. The file ZBGASM.CO has been added. To execute the Model 100 Debug/Assembler, position the cursor over ZBGASM.CO and press **ENTER**. The screen shows the startup message and the ZBUG prompt.

Note: the Model 100 Debug/Assembler occupies approximately 8.5K bytes of RAM. If you have other programs or files in memory, you may not be able to save ZBGASM. In this case, either load the Model 100 Debug/Assembler each time you wish to use it or delete some of your other files.

### CHAPTER 2/ RUNNING A SAMPLE PROGRAM

This "sample session" gets you started writing programs and shows how to use the Model 100 Debug/Assembler. The next chapters explain why the program works the way it does.

# 1. Start TEXT

Use the TEXT program to enter your assembly language programs. At the main menu, position the cursor over TEXT and press (ENTER).

TEXT prompts:

File to edit?

Type SAMPLE for this sample session.

TEXT then shows a blank screen with a flashing cursor at the top left corner of the screen.

# 2. Type the Source Program

Begin your assembly language program by typing:

TAB ORG TAB OCCOOH ENTER

The (TAB) key tabs to the next column. (ENTER) inserts the line into TEXT. The H means that the address CC00 is a hexadecimal number.

If you make a mistake, use the arrow keys to position the cursor at the mistake and type the correction. Use the **DEL** key if necessary. TEXT is described fully in your owner's manual, and a summary of Text Editor commands is in your *Model 100 Quick Reference Guide*.

Insert the entire assembly language program listed below.

|         | DRG  | ØCCØØH |

|---------|------|--------|

| HOME:   | CALL | 422DH  |

| SCREEN: | MVI  | A,ØFFH |

|         | CALL | 4B44H  |

| ROW:    | LDA  | ØF639H |

|         | CPI  | 8H     |

|         | JNZ  | SCREEN |

| COL:    | LDA  | ØF63AH |

|         | CPI  | 28H    |

|         | JNZ  | SCREEN |

| WAIT:   | CALL | 12CBH  |

| EXIT:   | CALL | 5797H  |

|         | END  | HOME   |

|         |      |        |

If you make a mistake, use TEXT's edit commands to correct it.

The program you have inserted is an assembly language "source" program, which we explain in the next chapter.

Press (F8) to exit TEXT. Your assembly language source program is automatically saved in RAM with the extension .DO.

# 3. Assemble the Source Program in Memory

If you saved ZBGASM as a RAM file, position the cursor over ZBGASM.CO and press (ENTER). This starts the Model 100 Debug/Assembler program. At the # prompt, type:

#### ASM SAMPLE.DO SAMPLE /WE (ENTER)

This loads the assembler program. The assembler then assembles your source program into 8085 machine code at the memory area just above ZBGASM. To let you know what it has done, it prints this listing:

| ; |        |      | ** ***            |         |      | •              |   |

|---|--------|------|-------------------|---------|------|----------------|---|

|   | CCØØ   |      |                   |         | ORG  | ØCCØØH         |   |

| 1 | CCØØ   | CD   | 422D              | HOME:   | CALL | 422DH          | I |

|   | CC03   | 3E   | FF                | SCREEN: | MVI  | A,ØFFH         | 1 |

|   | CCØ5   | CD   | 4B44              |         | CALL | 4B44H          | 1 |

|   | CC08   | ЗА   | F639              | ROW:    | LDA  | 0F639H         | ļ |

| 1 | CCØB   | FΕ   | 08                |         | CPI  | 8H             | 1 |

| ì | CCØD   | 02   | CC03              |         | JNZ  | SCREEN         | 1 |

| - | CC10   | ЗА   | F63A              | COL:    | LDA  | <b>0</b> F63AH |   |

|   | CC13   | FΕ   | 28                |         | CPI  | 28H            | 1 |

| 1 | CC15   | C2   | CCØ3              |         | JNZ  | SCREEN         |   |

|   | CC18   | CD   | 12CB              | WAIT:   | CALL | 12CBH          |   |

| I | CC1B   | CD   | 57 <del>9</del> 7 | EXIT:   | CALL | 5797H          | 1 |

|   |        |      | CCØØ              |         | END  | HOME           | 1 |

| 1 | 0000   | a ED | RORS              |         |      |                |   |

| ł | יששעשע |      | アロスシ              |         |      |                |   |

If the assembler does not print this entire listing but stops and shows an error message instead, you have an error in the source program. Repeat Steps 1 and 2.

When the assembly is complete, a new file is created called SAMPLE.CO. This file is the "object code" of your assembly language program.

The assembler commands are explained in Chapter 5, "Assembling the Program."

# 4. Run the Assembled Program

To run the assembled program, you need to be at the main menu. If you are at the # prompt, press  $\boxed{\textbf{F8}}$  to return to the menu.

Position the cursor over SAMPLE.CO and press **ENTER**. The SAMPLE program executes, filling the entire screen with a checkerboard of graphics characters.

Press (SPACEBAR) to exit the program and return to the main menu.

# 5. Debug the Program (if necessary)

ZBUG lets you look at memory. Load the Model 100 Debug/ Assembler again.

ZBGASM loads its ZBUG program and displays ZBUG's # prompt. You can now examine any memory address. Type:

ØCCØØH/

and ZBUG shows you what is in memory at this address. Press  $\bigcirc$  a few times to look at more memory addresses. When you finish, press  $\bigcirc$  ENTER.

In Chapter 8, we show you how to use ZBUG to examine and test your program. To exit the Model 100 Debug/Assembler, press (F8).

### **CHAPTER 3/ OVERVIEW**

The Model 100's 8085 processor understands only instructions written in 8085 machine code: a code of 0s and 1s containing "opcodes" and data. "Opcodes" are instructions that tell the processor to manipulate data in some way.

For example, the machine-code instruction "00111110 11111111" contains:

- The opcode "00111110" (decimal 62 or hexadecimal 3E)

- The data "11111111" (decimal 255 or hexadecimal FF)

ZBGASM looks for 3 fields in your instructions: label, command, and operand. For example, in this instruction:

HOME: CALL 422DH

HOME is the label (a colon delimiter must follow the label); CALL is the command; and 422DH is the operand.

In the label field, the Model 100 Debug/Assembler looks for:

• Symbols (symbolic names)

In the command field, it looks for:

- Mnemonics

- Pseudo Ops

In the operand field, it looks for:

- Symbols

- Operators

- Data

#### Symbols

A symbol is similar to a variable. It can represent a value or a location. HOME (in the sample session) is a symbol that represents the location of the instruction CALL 422DH. Operands can also be symbols. For example, in the instruction JNZ SCREEN, SCREEN is a symbol that represents the location of MVI A,0FFH.

#### **Mnemonics**

A mnemonic is a symbolic representation of an opcode. It is a command to the processor. "MVI" is a mnemonic. In the instruction MVI A,0FFH, MVI is the mnemonic for the opcode 00111110, which moves the data 0FFH (255) into Register A.

Mnemonics are specific to a particular processor. For example, if a computer uses a Z80 processor, it would understand only Z80 mnemonics, and not 8085 mnemonics.

#### Pseudo Ops

A pseudo op is a command to the assembler. END (in the sample session) is a pseudo op. It tells the assembler to quit assembling the program.

#### Data

Data is numbers or characters. Many mnemonics and pseudo ops call for data. Unless you use an operator (described next), the assembler interprets your data as a decimal (Base 10) number.

## **Operators**

An operator tells the assembler to perform a certain operation on the data. In the value 422DH the "H" is an operator. It tells the assembler that 422D is a hexadecimal (Base 16) number, rather than a decimal (Base 10) number.

The more commonly used operators are arithmetic and relational. Addition (+) and equation (=) are examples of these operators.

Pseudo ops, symbols, operators, and addressing-mode characters vary from one assembler to another. Section III explains them in detail.

# Sample Program

This is how each line in the sample program works:

ORG ØCCØØH

ORG is a pseudo op for "originate." It tells the assembler to begin loading the program at Location CC00H (Hexadecimal CC00). This means that when you load and run the program from the Model 100 main menu the program starts at Memory Address CC00H.

HOME: CALL 422DH

HOME is a symbol. It equals the location where the CALL 422DH instruction is stored.

CALL is a mnemonic that executes a subroutine. In this case, the routine being "called" is the Model 100 ROM routine to move the cursor to Row 1, Column 1 (home the cursor). The Model 100 ROM routines are listed in Reference Section F.

SCREEN: MVI A, ØFFH

SCREEN is a symbol. It equals the location where MVI A.0FFH is stored.

MVI is a mnemonic for "move immediate." It loads Register A with FFH, which is the hexadecimal ASCII code for a graphics character. Notice that the value FFH is preceded by a zero. All values that begin with a letter (A, B, C, D, E, F) must be preceded by a zero. The ASCII characters are listed in Reference Section G.

CALL 4B44H

This instruction calls the Model 100 ROM routine to display a character at the current cursor position.

ROW: LDA ØF639H

LDA is a mnemonic for "load Register A." It loads Register A with the hexadecimal address F639. This address contains the current row position of the cursor.

CPI 8H

CPI is the mnemonic for "compare immediate." It compares the value 8H to the contents of Register A. The maximum number of rows is 8.

JNZ SCREEN

JNZ is a mnemonic for "jump on not zero." If Register A does not equal 8H, the Z flag is not set, and the program jumps to the line labeled SCREEN. If Register A does equal 8H, the Z flag is set, and the program continues with the next line.

COL: LDA ØF63AH

This time, Register A is loaded with the current column position of the cursor (stored at address F63AH). COL: is the label.

CPI 28H

The contents of Register A are compared to 28H (40 decimal). This is the maximum number of characters per line.

JNZ SCREEN

If Register A does not equal 28H, the Z flag is not set, and the program jumps to the line labeled SCREEN. If Register A does equal 28H, the Z flag is set, and the program continues with the next line.

WAIT: CALL 12CBH

This line calls the ROM routine that "waits" until a character is input from the keyboard.

EXIT: CALL 5797H

After a key on the keyboard is pressed, the program exits by calling the ROM routine that displays the main menu.

END HOME

END is a pseudo op that tells the assembler to quit assembling the program. It also tells the assembler to store the beginning address of the program (the value of HOME).

# PART II/ COMMANDS

This section shows how to use the Model 100 Debug/Assembler commands. Knowing these commands will help you edit and test your program.

# CHAPTER 4/ EXAMINING MEMORY (ZBUG Commands — Part I)

To use the Model 100 Debug/Assembler, you must understand the Model 100's memory. You need to know about memory to write the program, assemble it, debug it, and execute it.

In this chapter, we explore memory and see some of the many ways to get information. To do this, we use ZBUG.

If you are not "in" ZBUG, with the ZBUG prompt (#) displayed, you need to get in it now.

Enter BASIC and load the Model 100 Debug/Assembler, then execute the program by typing:

CALL 54272 (ENTER)

The screen shows the ZBUG prompt (#) which means you are in ZBUG and can enter a command. You must enter all ZBUG commands at this level. You can return to the command level at any time by pressing **ENTER**).

## **Examining a Memory Location**

The 8085 can address 65,535 one-byte memory addresses, numbered 0-65535 (0000H-0FFFFH).

**Note:** Although the processor may address 65,535 addresses, the bottom 32,768 (7FFFH) are Read-Only-Memory (ROM) addresses and may not be changed.

We'll examine ROM Address OH. At the # prompt, type:

B ENTER

to get into the "byte mode." Then type:

ØH/

and the screen shows the contents of Address  $\emptyset$ . To see the contents of the next bytes, press 1. Use 1 to scroll to the preceding addresses.

Continue pressing ① or ①. Notice that as you use the ① the screen continues to scroll down. The smaller addresses are on the lower part of the screen.

All the numbers you see are hexadecimal (Base 16). You see not only the 10 numeric digits, but also the 6 alphabetic characters needed for Base 16 (A-F). Unless you specify another base (which we do in Chapter 6), ZBUG assumes you want to see Base 16 numbers.

Notice that a zero precedes all hexadecimal numbers that begin with an alphabetic character. This is to avoid any confusion between hexadecimal numbers and registers.

# **Examination Modes**

To help you interpret the contents of memory, ZBUG lets you examine it in four ways:

Examination Mode

Byte

B ENTER

Word

W ENTER

ASCII

A ENTER

Mnemonic

M ENTER

#### Byte Mode

Until now, you've been using the byte mode to examine memory. Typing B **ENTER** at the # prompt put you into this mode.

The byte mode displays every byte of memory as a number, whether it is part of a machine-language program or data.

In byte mode,  $\bigcirc$  increments the address by 1.  $\bigcirc$  decrements the address by 1.

#### Word Mode

Type **ENTER** to get back to the # prompt. To enter the word mode, type:

#### W ENTER

Look at the same memory address again. Press the  $\bigcirc$  key a few times. In this mode, the  $\bigcirc$  increments the address by 2. The numbers contained in each address are the same, but you see them 2 bytes or 1 word at a time.

Press the  $\bigcirc$  a few times. The  $\bigcirc$  always decrements the address by 1, regardless of the examination mode.

#### **ASCII Mode**

Return to the command level. To enter the ASCII mode, type:

## A ENTER

ZBUG now assumes the content of each memory address is an ASCII code. If the "code" is between 21H and 7FH, ZBUG displays the character it represents. Otherwise, it leaves the line following the address blank.

In the ASCII mode,  $\bigcirc$  increments the address by 1.

#### **Mnemonic Mode**

This is the default mode. Unless you specify some other mode, you are in the default mode.

Return to the # prompt. To enter the mnemonic mode from another mode, type:

M (ENTER)

Look at the lowest ROM addresses. Type:

ØH/

and, then press  $\bigcirc$  a few times. In the mnemonic mode, ZBUG assumes you're examining an assembly language program. The  $\bigcirc$  increments memory one to 5 bytes at a time (depending on the length of the instruction) by "disassembling" the numbers into the mnemonics they represent.

In our example, the first command—JMP 7D33—is a 3-byte instruction. Go into byte mode and list 3 bytes. The first byte (C3) is the opcode for the mnemonic JMP. The second byte (33) is the least significant byte of the address, and the third byte (7D) is the most significant byte of the address.

Note: In any instruction, the first byte always contains the opcode. In 3-byte instructions, the address is stored in the second and third bytes with the least significant byte of the address in the second byte and the most significant byte of the address in the third byte.

Begin the disassembly at a different byte. Press (ENTER) and then examine Address 1. Type:

1/

Even though you now see a different disassembly, the contents of memory have not actually changed. ZBUG is merely interpreting them differently.

For example, assume 1 contains a 33. This is really the low address byte of the JMP instruction. But when you begin disassembly at this location, ZBUG reads the first byte as an opcode. So 33 is interpreted as an INX SP instruction — and not as part of the address.

To see the program correctly, you must be sure you are beginning at the correct byte.

Sometimes, several bytes contain the symbol "??". This means ZBUG can't figure out which instruction is in that byte and is possibly disassembling from the wrong point. The only way to know you're on the right byte is to know where the program starts.

# **Changing Memory**

As you look at individual memory addresses, notice that the cursor remains to the right of the contents of each address. This lets you change the contents of that address. After typing the new contents, press **ENTER** or **(\*)**; the change is made. To make no changes, press **ENTER** or **(\*)**.

To show how to change memory, we'll open an address in memory above ROM and the HIMEM area. Get into the byte mode and open Address C000 by typing:

B ENTER ØCØØØH/ Notice that the cursor is to the right of the address. To put a l in that address, type:

#### 1 (ENTER)

If you want to change the contents of more than 1 address, type:

ØCØØ1H/

Then type:

ØDD 🕕

This changes the contents to DD and lets you change the next address. (Press 1 to verify that the change has been made.)

The size of the changes you can make depends on the examination mode. In the byte mode, you can change only 1 byte at a time and can type 1 or 2 digits.

In the word mode, you can change 1 word at a time. Any 1-, 2-, 3-, or 4-digit number you type becomes the new value of the word.

If you type a hexadecimal number that is also the name of an 8085 register (A,B,C,D,E,H,L,SP,PC), ZBUG assumes it's a register and gives you an "EXPression ERROR." To avoid this confusion, include a leading zero (0A,0B, etc.) whenever you enter hexadecimal numeric data that begins with a letter.

To change memory in the ASCII mode, use an apostrophe before the new letter. For example, here's how to write the letter C in memory at Address COOO. To get into the ASCII examination mode, type:

#### A ENTER

To open Address C000, type:

ØCØØØH/

To change its contents to a C, type:

'C (T)

Press 1 to confirm that the address contains the letter C.

If you are in mnemonic mode, you must change 1 to 5 bytes of memory depending on the length of the opcode. Changing memory is complex in mnemonic mode because you must type the opcodes rather than the mnemonic.

For example, get into the mnemonic mode and open Address C000. Type:

M ENTER 0C000H/

To change the instruction at this address to an ADD IMME-DIATE instruction, type:

C6 (ENTER)

Now Address 0C000H contains the opcode for the ADI mnemonic. Open location 0C001H:

ØCØØ1/

and insert 06, the operand:

Ø6 (ENTER)

Examine Address OCOOOH again, and you see it contains an ADI 6 instruction.

# CHAPTER 5/ ASSEMBLING THE PROGRAM (Assembler Commands)

To load the assembler program and assemble the source program into 8085 machine code, the Model 100 Debug/Assembler has an "assembly command." Depending on how you enter the command, the assembler:

- Shows an "assembly listing," which gives information on how the assembler is assembling the program.

- Stores the assembled program in a RAM file.

- Stores the assembled program on tape.

This chapter shows the different ways you can control the assembly listing and the in-memory assembly. Knowing this will help you debug a program.

## The Assembly Command

The command to assemble your source program into 8085 machine code is:

## Assembling in a RAM file:

$\underline{\mathsf{ASM}} \ <\! \mathit{source} \ \mathit{filename}\! > \ <\! \mathit{object} \ \mathit{filename}\! > \ /\! \mathit{SW1/SW2/...SWn}$

SW1, SW2, etc. are switches.

**Note:** If you omit the object filename, the object code is written to memory and not saved as a RAM file.

#### Assembling on tape:

ASM <source filename> CAS:<object filename> /SW1/...SWn

The assembled program is stored on tape under the same name as *source filename* if you do not use an object *filename*. Since source files must be RAM files created by the Text Editor (TEXT), they always carry the .DO extension.

The switch options are as follows:

| /LP | Assembly listing on the line printer |

|-----|--------------------------------------|

| /MR | Multiple record object code file     |

| /NL | No listing              |

|-----|-------------------------|

| /NO | No object code          |

| /NS | No symbol table         |

| /WE | Wait on assembly errors |

You may use any combination of the switch options. Be sure to include a blank space before the first switch.

### Examples:

ASM TEST.DO /WE

assembles the source program in memory and stops at each error (/WE).

ASM TEST.DO CAS: SAMPLE /LP

assembles the source program and saves it on tape as SAM-PLE. The listing is printed on the printer (/LP). Note that there must be a space between the *filename* and the /switch.

ASM TEST.DO CAS:

assembles the source program and saves it on tape as TEST.

#### ASM TEST.DO CAS: /MR

- - ·

assembles TEST.DO on cassette as a multiple record object code file. Normally, the Model 100 Debug/Assembler uses the same record format as BASIC's CSAVEM command to generate single record object code files on cassette.

Saving programs on cassette as single record files, however, has 2 drawbacks. First, since *all* data must be buffered before it can be written to cassette, buffer requirements may cause you to run out of memory. Second, the single record format doesn't let you generate non-contiguous object code. The /MR multiple record switch lets you overcome both of these restrictions.

**Note:** The multiple record feature applies only to cassette object files and not to RAM object files. Setting the /MR switch with an object file directed to RAM results in a DEVice Error.

You must load multiple record object files from the Debug/Assembler command level with the L load command. Trying to load a multiple record object file with the CLOADM command results in an OM (Out of Memory) Error.

# Controlling the Assembly Listing

The assembler normally displays an assembly listing similar to that on page 13. You can alter this listing with one of these switches:

/NS No symbol table in the listing

/NL No listing

/LP Listing printed on the printer

For example:

ASM TEST.DO /NS

assembles TEST.DO and shows a listing without the symbol table.

ASM SAMPLE.DO /LP

assembles SAMPLE.DO and prints the listing on the line printer.

Note: If the Model 100 Debug/Assembler displays an error message during a lengthy assembly listing, you may stop the listing by pressing SHIFT (BREAK). This command also terminates the assembly.

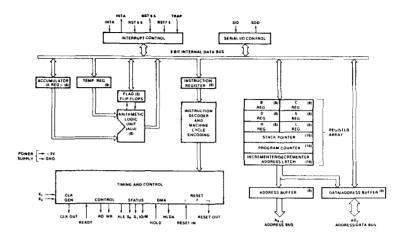

## **Memory Allocation**

ZBGASM uses approximately 8.5K of memory starting at 54272 (D400 Hex) and requires additional memory for the symbol table and object code buffer. The memory map (Figure 1) shows the Model 100 memory allocation after the Model 100 Debug/Assembler is loaded.

Available memory is defined as the memory beginning at Himem+l and extending up to the start of the symbol table. Memory outside this range is considered "restricted." Any operation that results in a modification of restricted memory causes an

MRM?

warning message. This message alerts you that your operation modifies restricted memory and asks for confirmation to continue. A "Y" response to the MRM? message allows the change (if the modification is not in ROM); a (CTRL)Y response allows the change and cancels further MRM? warnings (if the modification is not in ROM). Any other responses terminate the operation.

|                    | MEMORY MAP         |

|--------------------|--------------------|

| FFFF               | BASIC/SYSTEM TEMPS |

| F5F0               | BASIC/STSTEM TEMPS |

| D400               | ZBGASM             |

|                    | SYMBOL TABLE       |

|                    |                    |

| [LOMEM]<br>[HIMEN] | OBJECT CODE        |

|                    | BASIC STORAGE      |

| 8000               | RAM FILES          |

| 7FFF               | BASIC ROM          |

| 0000               |                    |

FIGURE 1

Warning: Exercise extreme care when modifying restricted memory. Know exactly what you are modifying and the consequences of the modification. Some changes in restricted memory can result in the loss of all your RAM files.

As shown in the memory map, the symbol table is built down from the start of ZBGASM. The lower portion of available memory (beginning at Himem+l and extending to the start of the symbol table) is used for the object code generated by in-memory assemblies and for buffering the object code to be written to a cassette file. Insufficient available memory for the above operations results in an OM (Out of Memory) Error.

You can control the amount of available memory allocated to ZBGASM by using the CLEAR statement to set the BASIC HIMEM parameter. (See your Model 100 owner's manual for details on this procedure.)

The lower the address you assign to Himem, the more available memory you allocate to ZBGASM. Lower Himem addresses, however, decrease the space available for RAM files, and may cause you to overwrite or limit RAM files.

## Hints On Assembly

- Use a symbolic name to label the beginning of your program.

- The /WE switch is an excellent debugging tool. Use it to detect assembly errors before debugging the program.

- To examine the symbol table or any other location after an assembly, use ZBUG.

# CHAPTER 6/ DEBUGGING THE PROGRAM (ZBUG Commands — Part II)

ZBUG has some powerful tools for a trial run of your assembled program. You can use them to look at each register, every flag, and every memory address during every step of running the program.

Before reading any further, you might want to review the ZBUG commands you learned in Chapter 4. We use these commands here.

# Preparing the Program for ZBUG

In this chapter, we use the sample program from Chapter 2 to show how to test a program.

First, load and then enter ZBUG.

Next, assemble SAMPLE.DO into ZBGASM.

When the # prompt appears, you're ready to test the sample program with ZBUG.

# **Display Modes**

In Chapter 4, we discussed 4 examination modes. ZBUG also has 3 display modes.

We'll examine each of these display modes from the mnemonic examination mode. If you're not in this mode, type M (ENTER) to get into it.

#### **Numeric Mode**

Type:

N (ENTER)

and examine the memory addresses that contain your program: CC00H-CC13H.

In the numeric mode, you do not see any of the symbols (labels) in your program (SCREEN, ROW, WAIT, EXIT, etc.). All you see are numbers. For example, Address CCODH shows the instruction JNZ OCCO3 rather than JNZ SCREEN.

#### Symbolic Mode

From the command level, type:

#### S (ENTER)

and examine your program again. ZBUG displays your entire program in terms of its symbols (SCREEN, WAIT, ROW, CALL, WAIT, etc.). Examine the memory address containing the JNZ SCREEN instruction by typing the memory address of the previous instruction:

#### ØCCØBH/

Now press (1). In the symbolic mode, the screen shows your program's memory addresses and instructions as symbols (labels):

ROW+5/ JNZ SCREEN

# Half-Symbolic Mode

At the # prompt, type:

H ENTER

and examine the program. Now all the memory addresses (on the left) are shown as symbols, but the operands (on the right) are shown as numbers.

# **Using Symbols to Examine Memory**

Since ZBUG understands symbols, you can use them in your commands. For example, with ZBUG, both of the following commands open the same memory address regardless of the display mode:

HOME /

or

ØCCØØH/

Both these commands get ZBUG to display your entire program:

T HOME EXIT

Note: ZBUG usually directs console output to the LCD screen. Use the K (console change) command to redirect a listing (or any other output) to your printer or communications port. (See Reference Section B for details on using the K command.)

# **Executing the Program**

You can run your program from ZBUG using the G (Go) command followed by the program's start address.

Type either of the following:

- G HOME (ENTER)

- G OCCOOH ENTER

The program executes, filling all of your screen with a pattern of graphics characters. If you don't get this pattern, the program probably has a "bug." The rest of the chapter discusses program bugs.

#### **Setting Breakpoints**

If your program doesn't work properly, you might find it easier to debug it if you break it up into small units and run each unit separately. The X command sets breakpoints at which ZBUG pauses during the execution of a program. From the command level, type:

X

followed by the address where you want execution to break.

We'll set a breakpoint at the first address that contains the symbol SCREEN: C003H.

Type either of the following:

XSCREEN ENTER XCC03 (ENTER)

Now type GHOME ENTER to execute the program. Each time execution breaks, type:

#### C (ENTER)

to continue. A graphics character appears on the screen each time ZBUG executes the SCREEN loop. The line:

#### Ø BRK @ SCREEN

follows the graphics character to tell you that Breakpoint 0 is set at the SCREEN address. You may set up to 8 breakpoints numbered from 0-7 in a program.

Type:

#### D (ENTER)

to display all the breakpoints you have set.

Type:

# C10 (ENTER)

ZBUG continues until the tenth time it encounters that breakpoint, and then halts execution. Type:

# Y ENTER

This is the command to "yank" (delete) all breakpoints. You can also delete a specific breakpoint. For example:

# YØ ENTER

deletes the first breakpoint (Breakpoint 0).

You may not set a breakpoint in a ROM routine. Also, if you set a breakpoint at the point where you call a ROM routine, the C command returns a CONtinuation Error and doesn't let you continue the program.

# **Examining Registers and Flags**

# Assemble SAMPLE.DO, and type:

#### R (ENTER)

What you see are the contents of every register before the program is executed. (See Chapter 8 for a definition of all the 8085 registers and flags.)

Your display should look something like this:

PC SP BC DE HL A F 0000 F569 0000 0000 0000 000

Type:

ØCCØØH;

The semicolon (;) executes the instruction at memory address CC00 and displays the next line.

Type; again to execute the instruction at CC03. Now look at all the registers by typing

# R (ENTER)

The Accumulator (Register A) now contains FF (the ASCII code for a graphics character) from the MOV A, ØFFH instruction.

To display only the contents of Register B, type:

B/

To display the register pair HL, type:

HL/

Now it contains a 0. You can change registers in the same way you change the contents of memory. With the cursor on the same line as HL/ 0, type:

1234 **ENTER**

Check the HL Register pair to verify that it contains 1234.

# Stepping Through the Program

Type:

SCREEN;

CALL 422DH is the next instruction to be executed. The first instruction, MVI A,0FFH, has just been executed. To see the next instruction, type:

;

Now, CALL 422DH has been executed, and LDA 0F639H is the next instruction. Type:

;

To see that the LDA instruction was executed, type:

R **ENTER**

Register A now contains the current row position of the cursor. (Memory address F639H is a status location that contains the current row position of the cursor.)

Use the semicolon and R command to continue to single-step through the program examining the registers at will.

You may also single-step through a program using a comma (,) instead of a semicolon. The comma, however, cannot step through a ROM subroutine. For example, type:

RDW,

Continue stepping through the program by repeatedly pressing comma. When you reach the CALL 4B44H instruction, the screen shows a CONtinuation Error because you are trying to CALL a ROM subroutine.

# Transferring a Block of Memory

Type:

U ØCCØØH ØCØØØH 5 (ENTER)

Now the first 5 bytes of your program have been copied to memory address beginning at COO.

# Hints on Debugging

- Don't expect your first program to work the first time. Have patience. Most new programs have bugs. Debugging is a fact of life for all programmers, not just beginners.

- Be sure to make a copy of what you have in the edit buffer before executing the program. The edit buffer is not protected from machine language programs.

# CHAPTER 7/ USING THE ZBUG CALCULATOR (ZBUG Commands — Part III)

ZBUG has a built-in calculator that performs arithmetic, relational, and logical operations. Also, it lets you use 3 different numbering systems, ASCII characters, and symbols.

This chapter contains examples of how to use the calculator. Some use the same assembled program that we used in the last chapter.

# **Numbering System Modes**

ZBUG recognizes numbers in 3 numbering systems: hexadecimal (Base 16), decimal (Base 10), and octal (Base 8).

#### **Output Mode**

The output mode determines which numbering system ZBUG uses to output (display) numbers. From the ZBUG command level, type:

# 010 ENTER

Examine memory. The T at the end of each number stands for Base 10. Type:

# D8 (ENTER)

Examine memory. The Q at the end of each number stands for Base 8. Type:

# 016 (ENTER)

You're now back in Base 16, the default output mode.

# Input Mode

You can change input modes in the same way you change output modes. For example, type:

#### I 10 (ENTER)

Now, ZBUG interprets any number you input as a Base 10 number. For example, if you are in this mode and type:

#### T 49152 49162 (ENTER)

ZSBUG shows you memory addresses 49152 (Base 10) through 49162 (Base 10). Note that what is printed on the screen is determined by the output mode, not the input mode.

You can use these special characters to "override" your input mode:

| BASE    | BEFORE NUMBER | AFTER NUMBER |

|---------|---------------|--------------|

| Base 10 | &             | Т            |

| Base 16 | #             | Н            |

| Base 8  | @             | Q            |

Table 1. Special Input Mode Characters

For example, while still in the I10 mode, type:

# T 49152 #00010 (ENTER)

The "#" overrides the I10 mode. ZBUG, therefore, interprets C010 as a hexadecimal number. As another example, get into the I16 mode and type:

T 49152T ØCØ1Ø (ENTER)

Here, the "T" overrides the I16 mode. ZBUG interprets 49152 as decimal.

# **Operations**

ZBUG performs many kinds of operations for you. For example, type:

and ZBUG goes to memory address C019 (Base 16), the sum of C000 (Base 16) and 25 (Base 10). If you simply want ZBUG to print the results of this calculation, type:

On the following pages, we use the terms operands, operators, and operation. An operation is any calculation you want ZBUG to solve. In this operation:

$$1 + 2 =$$

"1" and "2" are the operands. "+" is the operator.

# **Operands**

You may use any of these as operands:

- 1. ASCII characters

- 2. Symbols

- 3. Numbers (in either Base 8, 10, or 16).

**Note:** ZBUG recognizes integers (whole numbers) only.

Examples (in the O16 output mode):

' A =

prints 41, the ASCII code for "A".

HOME =

prints the HOME address of the sample program. (It will print UDS Error [Undefined Symbol Error] if you don't have the sample program assembled in memory.)

15Q=

prints the hexadecimal equivalent of octal 15.

If you want your results printed in a different numbering system, use a different output mode. For example, get into the Ol0 mode and try the above examples again.

# **Operators**

Negative

You may use arithmetic, relational, or logical operators. (Get into the O16 mode for the following examples.)

Arithmetic Operators

Addition +

Subtraction Multiplication \*

Division .DIV.

Modulus .MOD.

Positive +

43

# Examples:

EXIT-HOME =

prints the length of the sample program (not including the END statement).

9.DIV.2=

prints 4. (ZBUG can divide integers only.)

9.MDD.2=

prints 1, the remainder of 9 divided by 2.

1-2=

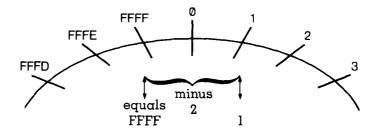

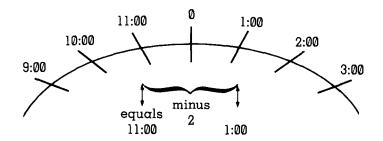

prints OFFFF,65535T, or 177777Q, depending on the output mode. ZBUG does not use negative numbers. Instead, it uses a "number circle" that operates on modulus 10000 (hexadecimal):

# Number Circle Illustration of Memory

To understand this number circle, you can use the clock as an analogy. A clock operates on modulus 12 in the same way the ZBUG operates on modulus 10000. Therefore, on a clock, 1:00 minus 2 equals 11:00:

Number Circle Illustration of Clock

#### **Relational Operators**

Equal to .EQU. Not Equal to .NEQ.

These operators determine whether  $\alpha$  relationship is true or false.

# Examples:

5.EQU.5=

prints 0FFFF, since the relationship is true. (ZBUG prints 65535T in the O10 mode or 177777Q in the O8 mode.)

5.NEQ.5=

prints  $\ensuremath{\mathbf{0}}$ , since the relationship is false.

# **Logical Operators**

| Shift       | <     |

|-------------|-------|

| LogicalAND  | .AND. |

| InclusiveOR | .OR.  |

| ExclusiveOR | .XOR. |

| Complement  | .NOT. |

Logical operators perform bit manipulation on binary numbers.

# Examples:

shifts 10 two bits to the left to equal 40. The 8085 RLC instruction also performs this operation.

shifts 10 two bits to the right to equal 4. The 8085 RRC instruction also performs this operation.

prints 3, the Exclusive OR of 6 and 5. The 8085 XOR instruction also performs this operation.

# **Complex Operations**

ZBUG calculates complex operations in this order of precedence:

You may use parentheses to change this order.

Examples:

$$4 + 4.DIV.2 =$$

The division is performed first.

$$(4+4).DIV.2 =$$

The addition is performed first.

$$\mathbf{4}^{\star}\mathbf{4}.DIV.\mathbf{4} =$$

The multiplication is performed first.

# PART III/ ASSEMBLY LANGUAGE

This section gives details on 8085 assembly language. It does not explain the 8085 mnemonics, however, since there are many books available on the 8080 family of microprocessors.

# **CHAPTER 8/ WRITING THE PROGRAM**

Chapter 3 gives a general description of assembly language instructions. This chapter describes them in detail.

# The 8085 Registers

The 8085 contains 10 temporary storage areas (registers) that you may use in your program:

**Register A** manipulates data and performs arithmetic and logical calculations. It holds 1 byte of data.

Register Pair H-L are used for direct addressing. H stores the most significant byte of an address, Register L stores the least significant byte of an address. This lets the processor directly access an address with the single, least significant byte.

Register Pairs B-C and D-E can each hold 2 bytes of data. They are general purpose registers and may be used for temporary data storage. They may be used individually to hold 1-byte data.

Register PC (Program Counter) stores the address of the next instruction to be executed.

Note: The current address of Register PC may be represented in ZBUG by using a \$ or . in the operand field.

Register SP (Stack Pointer) is a 16-bit register that points to the memory stack. Addresses are stored in the stack in a "last-in, first-out" manner. The last address put into the stack should be the first address to be pulled.

Status Register F is the Flag register for testing conditions and setting interrupts. It consists of 5 "flags." Many mnemonics "set" or "clear" 1 or more of these flags. Others test to see if a certain flag is set or clear.

This is the meaning of each flag, if set:

Bit 0

CY (Carry) — an 8-bit arithmetic operation caused a carry or borrow from the most significant bit.

Bit 1

Reserved

Bit 2

P (Parity) — the result of the previous operation has an even number of bits set (even parity).

Bit 3

Reserved

Bit 4

AC (Auxiliary Carry or Half Carry) — an 8-bit addition operation caused a carry.

Bit 5

Reserved

Bit 6

Z (Zero) — the result of the previous operation is zero.

Bit 7

${\bf S}$  (Sign) — the result of the previous operation is a negative number

# **Assembly Language Fields**

You may use 4 fields in an assembly language instruction: label, command, operand, comment. In this instruction:

HOME: MOV A,M

; MOVES MEMORY DATA TO REGA

HOME is the label. MOV is the command. A,M is the operand. MOVES MEMORY DATA TO REG A is the comment.

The comment is solely for your convenience. The assembler ignores comments after a semicolon.

#### The Label

You can use a symbol in the label field to define a memory address or data. The above instruction uses HOME to define its memory address.

Once the address is defined, you can use HOME as an operand in other instructions. For example:

#### JNZ HOME

branches to the memory address defined by HOME.

The assembler stores all the symbols, with the addresses or data they define, in a "symbol table," rather than as part of the "executable program." The symbol can be a maximum of 6 characters.

#### The Command

The command can be either a pseudo op or a mnemonic.

Pseudo ops are commands to the assembler. The assembler does not translate them into opcodes and does not store them with the executable program. For example:

NAME:

**EQU**

43

defines the symbol NAME as 43. The assembler stores this in its symbol table.

ORG

0CC00H

is a pseudo op that tells the assembler to begin the executable program at Address CC00.

SYMBOL:

DC

6

stores 6 in the current memory address and labels this address SYMBOL. The assembler stores this information in its symbol table.

Mnemonics are commands to the processor. The assembler translates them into opcodes and stores them with the executable program. For example:

#### **XCHG**

tells the processor to exchange the data in the H-L Register Pair with the D-E Register Pair. The assembler assembles this into opcode number EBH and stores it with the executable program.

The next chapter shows how to use pseudo ops. Reference G lists the 8085 mnemonics.

# The Operand

The operand is either a memory address or data. For example:

LXI BC, 3000 + COUNT

loads Register Pair B-C with 3000H plus the value of COUNT. The operand, 3000+COUNT, specifies a data constant.

The assembler stores the operand with its opcode. Both are stored with the executable program.

#### Operators

The plus sign (+) in the above operand (3000 + COUNT) is called an operator.

You can use any operator described in *Chapter 7*, "Using the ZBUG Calculator," as part of the operand.

# Addressing Modes

8085 mnemonics have 4 addressing modes that let you address data in different ways.

# 1. Immediate Addressing

The operand is data. For example:

ADI

30H

adds the value 30H to the contents of Register A.

DATA:

EQU LXI 8004H

I BC,DATA

loads the value 8004 into Register Pair BC.

CPI

94H

compares the contents of Register A with the hexadecimal value 94.

# 2. Direct Addressing

The operand is the exact memory address of the data. In this mode of addressing, you address a specific memory location.

For example:

INZ

0CC00H

jumps to Address CC00.

SPOT:

EQU

0CC00H

SHLD

SPOT

stores the contents of Register Pair HL in Address CC00.

If the instruction calls for data, the operand contains the address where the data is stored.

LHLD

0CC00H

does not load Register Pair HL with CC00. The processor loads HL with whatever data is in Address CC00. If 65H is stored in Address CC00, Register Pair HL is loaded with 65H.

#### ADD M

adds whatever data is stored in the Address in the HL Register Pair to the contents of Register A.

#### 3. Register Indirect Addressing.

The operand is the HL Register Pair that contains the *address* in memory that contains the data.

In understanding this mode, think of a treasure hunt game. The first instruction is "Look in the suitcase." The suitcase contains the second instruction, "Look in the mailbox."

Examples:

#### MOV A,M

moves the contents of the memory location whose address is in Register pair HL. M refers to the memory address currently stored in Register Pair HL.

The following example shows the complete process:

| LXI  | HL,0CC00H |

|------|-----------|

| MVI  | M,0FFH    |

| INX  | Н         |

| MVI  | M,0FFH    |

|      |           |

|      | 0.000011  |

| LHLD | 0CC00H    |

| MOV  | A,M       |

The LXI instruction loads address CCOO into the H-L Register Pair, and MVI moves the data FF into Register L. The INX instruction increments the address in the H-L Register Pair by 1, and MVI moves the data FF into memory location CCO1.

Later in the program, you can access the data FFFF by loading memory location CC00 into the H-L Register Pair and then moving the data into the accumulator.

This is a good mode of addressing to use when calling ROM routines.

#### 4. Register Addressing

This addressing mode lets you access data by specifying registers or register pairs containing the data. The operand is always a register.

For example:

#### MOV A.B

transfers the data in Register B to Register A. Now both of the registers contain the same data.

Register pairs may also be addressed:

#### DAD BC

adds the data in Register Pair BC to the data in Register Pair HL. The result is placed in HL.

# CHAPTER 9/ USING PSEUDO OPS

As discussed earlier, pseudo ops direct the assembler. You can use them to:

- Control where the program is assembled

- Define symbols

- Insert data into the program

- · Change the assembly listing

- Do a "conditional" assembly

- Include another source file in your program

Pseudo ops are unique to the assembler you are using. Other 8085 assemblers may not recognize the ZBUG pseudo ops.

The ZBUG pseudo ops make it easier for you to program. This chapter shows how to use pseudo ops.

# Controlling Where the Program is Assembled

ZBUG has two pseudo ops that control where the program is assembled:

- ORG, sets the first location

- END, ends the assembly

#### ORG

# ORG expression

Tells the assembler to begin assembling the program at expression. Example:

ORG

0CC00H

tells the assembler to start assembling the program at Address CCOO.

You can put more than one ORG command in a program. When the assembler arrives at the new ORG, it begins assembling at the new expression.

**Note:** \$ or . may be used as an operand to return the current location of the program counter. ORG \$+50, for example, opens 50 bytes between the present location and the next assembled location.

#### **END**

#### END expression

Tells the assembler to quit assembling the program. The expression option lets you store the program's start address. Use END as the last instruction in all your assembly language programs.

# Example:

| HOME: | ORG<br>MOV | 0CC00H<br>A,M          |

|-------|------------|------------------------|

|       | •          |                        |

| DATA: | DC<br>END  | 'This is data'<br>HOME |

The END pseudo op quits the assembly and stores the program's entry address (the value of HOME) in memory. When you load the program, the processor knows to start executing at HOME (the LDA instruction) rather than at DATA (the DC instruction).

DC is a pseudo op explained later in this chapter.

# **Defining Symbols**

Symbols make it easy to write a program and also make the program easy to read and revise. The ZBUG has 2 pseudo ops for defining symbols:

- EQU, for defining a constant value

- · SET, for defining a variable value

# **EQU**

symbol EQU expression

Equates symbol to expression. Examples:

CHAR:

EQU

F9H

makes every use of CHAR equal to F9H.

KYREAD:

EQU

7242H

CALL

KYREAD

equates KYREAD to 7242H. The next instruction calls the ROM routine at memory address 7242H.

EQU helps set the values of constants. You can use it anywhere in your program.

#### SET

#### symbol SET expression

Sets *symbol* equal to *expression*. You can use SET to reset the symbol elsewhere in the program. Example:

SYMBOL:

SET

25

sets SYMBOL equal to 25. Later in the program, you can reset SYMBOL.

SYMBOL: SET SYMBOL + COUNT

Now SYMBOL equals 25 + COUNT.

# Inserting Data into Your Program

ZBUG has 4 pseudo ops that make it simple for you to reserve memory and insert data in your program:

- DS, for reserving areas of memory for data

- DB, for inserting 1 byte of data in memory

- DW, for inserting 2 bytes of data in memory

- DC, for inserting a string of data in memory

Remember that the processor cannot "execute" a block of data in your program. If you use these pseudo ops:

- Use them at the end of your program (just before the END instruction), or

- Precede them with an instruction that jumps or branches to the next 'executable' instruction.

#### DS

#### symbol DS expression

(Define Storage) Reserves *expression* bytes of memory for data. Example:

BUFFER:

DS

200

reserves 200 bytes for data, starting at Address BUFFER.

DATA:

DS

6+SYMBOL

reserves 6+SYMBOL bytes for data beginning at Address DATA.

#### DB

# symbol DB expression

(Define Byte) Stores a 1-byte expression in memory at the current address. The symbol is optional.

Examples:

DATA:

DB

33H

stores 33H in Address DATA.

FACTOR:

DB

NUM/2 FACTOR

LDA

stores NUM/2 in Address FACTOR and then loads NUM/2 into Register  $\overline{A}$ .

#### DW

# symbol DW expression

(Define Word) Stores a 2-byte expression in memory starting at the current address. The symbol is optional. Example:

DATA:

DW

1100H

stores 1100H in Address DATA and DATA + 1.

#### DC

# symbol DC delimiter string delimiter

Stores an ASCII string in memory, beginning at the current address. The *symbol* is optional. The *delimiter* can be any character.

Examples:

TABLE: DC /THIS IS A STRING/

stores the ASCII codes for THIS IS A STRING in memory locations, beginning with TABLE.

|       | •                                |                              |

|-------|----------------------------------|------------------------------|

| INIT: | LXI<br>MVI                       | H,NAME<br>B,4                |

|       | •                                |                              |

| DISP: | MOV<br>CALL<br>INX<br>DCR<br>JNZ | A,M<br>LCD<br>H<br>B<br>DISP |

| NAME: | DC<br>DB                         | 'GARY'<br>0DH                |

The first instruction loads NAME into Register Pair HL. The pseudo op DC at the end of the program stores "Gary" in the four memory addresses beginning with NAME. The DISP routine processes this data.

# **PART IV/ ROM ROUTINES**

In an assembly language program, the simplest way to use the I/O devices is with ROM routines.

This section shows how. A complete list of ROM routines is in Reference Section E.

# CHAPTER 10/ USING THE KEYBOARD AND VIDEO DISPLAY (ROM ROUTINES)

The Model 100 uses its own machine-code routines to access the screen, keyboard, and tape. These routines are built into the computer's ROM. You can use the same routines in your own program.

Appendix F lists each ROM routine and the ROM address that points to it. This chapter uses 2 of these routines, CHGET and LCD, as samples in showing the steps for using ROM routines.

# **Steps for Calling ROM Routines**

We recommend these steps for calling a ROM routine:

- 1. Equate the routine's address to its name. This lets you refer to the routine by its name rather than its address, making your program easier to read and revise.

- 2. Set up any entry conditions required by the routine. This lets you pass data to the routine.

- Preserve the contents of the registers. Since many routines change the contents of the registers, you might want to store the registers' contents temporarily before jumping to the routine.

- 4. Call the ROM routine, using the indirect addressing mode.

- 5. Use any exit conditions that the routine passes back to your program.

- 6. Restore the contents of the registers (if you temporarily preserved them in Step 3).

# Sample: Keyboard Input with CHGET

This short program uses 4 ROM subroutines to (1) "home" the cursor, (2) monitor the keyboard, (3) display characters, and (4) exit to the menu. Each key you press is displayed until you press (RETURN) which returns you to the main menu.

CHGET monitors the keyboard and waits for you press a key. When you do press a key, CHGET loads Register A with the key's ASCII code. LCD then displays the contents of Register A on the screen.

```

DRG

ØCCØØH

HOME:

EQU

422DH

;ROM routine homes cursor

CHGET:

EQU

12CDH

ROM routine waits for a key

LCD:

EQU

4B44H

;ROM routine displays character

EXIT:

EQU

5797H

;ROM exit routine

BEGIN:

PUSH

PSW

;store Registers A and F data

LOOP:

CALL

CHGET

CALL

LCD

CPI

Ø DH

;Look for a carriage return

LOOP

JNZ

; If no (ENTER) loop to LOOP

POP

PSW

restore Registers A and F data

CALL

EXIT

END

BEGIN

```

This is how we applied the above steps in writing this program:

# 1. Equate ROM routines to their Addresses

This equates CHGET to 12CBH, the address that points to CHGET's address:

CHGET:

EQU

12CBH

# 2. Set Up Entry Conditions

HOME, CHGET, and EXIT have no entry conditions. LCD requires that Register A contains the character to be displayed. CHGET fulfills the entry requirement for LCD.

#### 3. Preserve the Registers' Contents

Only Registers A and F (Carry Flag) are affected by the program. This preserves the contents of Register A and all the condition flags:

BEGIN:

**PUSH**

**PSW**

This instruction "pushes" the value of Register A into a memory location 1 less than the SP Register, and pushes the condition flags (Register F) into a memory location 2 less than the SP Register.

#### 4. Call ROM routines

This CALLs CHGET:

LOOP:

CALL

CHGET

This displays the character you typed onto the LCD screen:

CALL LCD

#### 5. Use Exit Conditions

After the CHGET subroutine is executed, Register A contains a character. That character is compared to a carriage return:

CPI

0DH

The above instruction branches back to LOOP (the JNZ LOOP instruction) if you do not press (RETURN). (Pressing (RETURN) calls the EXIT subroutine.

# 6. Restore the Register's Contents

This "pops" (restores) the contents of Registers A and F:

POP

**PSW**

Now, the above registers are restored to the data they contained before executing the CHGET routine.

# 7. Exit the Program

This CALLs the Exit Routine that lets you properly exit the program and return to the Model 100's main menu screen:

CALL

EXIT

E. 546

# PART V/ REFERENCE

This section summarizes all the features of the Model 100 Debug/Assembler.

### REFERENCE A/ ASSEMBLER COMMANDS AND SWITCHES

### ASM source filename object filename /switch/. . .

Assembles the source program into machine code in memory. Source files must be RAM files generated by the Text Editor (TEXT) and therefore always carry the .DO extension. The source filename is always required. If the object code filename is omitted, the object code is written directly to memory and no object file is created.

### ASM source filename CAS:object filename /switch/. . .

Assembles the source program into machine code in the cassette. When the device specifier CAS: precedes the object filename, the object file is created and written to the cassette recorder. If the object filename is omitted, the source filename is assigned to the object file.

#### The assembler switches are:

| /LP | Assembly listing on the printer. |

|-----|----------------------------------|

| /MR | Multiple record object code file |

| /NL | No listing printed.              |

| /NO | No object code generated.        |

| /NS | No symbol table generated.       |

| /WE | Wait on assembly errors.         |

### Examples:

ASM SAMPLE.DO SAMPLE ASM TEST.DO CAS:TEST /WE ASM TEST.DO /NO/NS

### REFERENCE B/ ZBUG COMMANDS

The following list defines the terms used in this section:

#### expression

One or more numbers, symbols, or ASCII characters. If more than one is used, you may separate them with these operators:

| Multiplication | *     | Addition    | +     |

|----------------|-------|-------------|-------|

| Division       | .DIV. | Subtraction | -     |

| Modulus        | .MOD. | Equals      | .EQU. |

| Shift          | <     | Not Equal   | .NEG. |

| Local And      | .AND. | Positive    | +     |

| Exclusive Or   | .XOR. | Negative    | -     |

| Logical Or     | .OR.  | Complement  | .NOT. |

#### address

A location in memory. This may be specified as an expression using numbers or symbols.

#### filename

A BASIC cassette file specification.

### Commands

C

### CONTINUE FROM BREAKPOINT C expression ENTER

Continues execution of the program after interruption at a breakpoint. The expression specifies the proceed count, which is the number of times (-1) that the breakpoint will be passed before a break occurs. Numbers in the expression for the proceed count are interpreted as decimal numbers regardless of the input radix setting.

### C(ENTER)

Continue by increments of 1.

D

DISPLAY BREAKPOINTS D (ENTER)

Displays all breakpoints that have been set.

#### G

GO EXECUTE G expression ENTER

Executes the program beginning at the address specified by the *expression*. The expression is required.

### K

### CONSOLE CHANGE K ENTER

The Debug/Assembler usually directs console output to the LCD. The K command allows you to direct the console output to any of 3 devices—screen, printer, communications—by responding to the LCD=0 LPT=1 COM=2 CNS= prompt with the appropriate number.

#### L

LOAD A MACHINE LANGUAGE FILE L filename (ENTER) Loads a machine language file filename from RAM files. Using CAS: to specify the cassette recorder—L CAS: filename (ENTER)—loads a machine language file filename from cassette.

#### CL

CASSETTE LOAD A MACHINE LANGUAGE FILE

CL filename **ENTER**

Loads machine language file filename from cassette.

#### F

PUNCH filename start address end address execution address

Saves memory from start address to end address in a RAM file. You must also specify an execution address, the first address to be executed when the file is loaded. Using CAS: to specify the cassette recorder—P CAS: filename start address end address execution address—saves memory from start address to end address in cassette.

#### CP

CASSETTE PUNCH filename start address end address execution address

Saves memory to cassette from *start address* to *end address*. You must also specify an *execution address*, the first address to be executed when the file is loaded.

#### R

REGISTER DISPLAY R (ENTER)

Displays the contents of all the registers.

#### T

TYPE OUT T address1 address2 (ENTER)

Displays the memory locations from address1 to address2, inclusive. Uses the current Examination and Type Out Modes.

#### U

BLOCK TRANSFER U source address destination address byte count

Transfers the contents of memory beginning at source address and continuing for count bytes to another location in memory beginning with destination address.

### X

SET BREAKPOINT X address ENTER

Sets a breakpoint at address. If address is omitted, the current location is used. Each breakpoint is assigned a number from  $\emptyset$  to 7. The first breakpoint set is assigned as Breakpoint  $\emptyset$ . A maximum of eight breakpoints may be set at one time.

#### Υ

YANK BREAKPOINT Y n ENTER

Deletes the breakpoint referenced by the n number (0-7). If n is omitted, all breakpoints are deleted.

#### Z

DELETE SYMBOL TABLE Z (ENTER)

Deletes the current symbol table.

### **Examination Mode Commands**

A ENTER ASCII Mode

B ENTER Byte Mode

M (ENTER) Mnemonic Mode

W (ENTER) Word Mode

(The default is M)

### **Display Mode Commands**

H ENTER

Half Symbolic

N ENTER

S ENTER

Numberic Symbolic

(The default is S)

### **Numbering System Mode Commands**

Obase

Output

Ibase

Input

(Base can be 8, 10, or 16. The default is 16)

### **Special Symbols**

/

OPEN A LOCATION address/

Opens the specified memory location. Opens the current location if address is omitted.

OPEN NEXT LOCATION

$\odot$

Opens next address and allows you to enter any change.

**①**

OPEN PRECEDING LOCATION

$\odot$

Opens preceding address and allows you to enter any changes.

address **ENTER**

register

OPEN A REGISTER AT AN ADDRESS address/ register/

Opens address of register and displays its contents. If address is omitted, the register at the last address is reopened. After the contents have been displayed, you may type:

new value

To change the contents.

(ENTER)

To close and enter any change.

### SINGLE STEP EXECUTION address.

Executes the instruction at a specific memory address. A, without an address executes the instruction at the current setting of the Program Counter (PC).

### SINGLE STEP EXECUTION—SKIP SUBROUTINES

Executes the instruction at the current setting of the Program Counter, but skips all subroutines except CALL. When : encounters a CALL, it executes the entire subroutine.

#### FORCE FLAGS

Opens the current location, forcing the flags mode. The colon does not actually have anything to do with the (status flag) Register F. It simply interprets the contents of the given address as if it contained flag bits.

#### =

### EVALUATE THE EXPRESSION expressions=

Opens the current memory location and forces the numeric type out mode and byte examination mode to evaluate the expression.

### REFERENCE C/ DEBUG/ASSEMBLER ERROR MESSAGES

These are error messages you can get while in ZBGASM:

BAS BASIC Error (General)

BASIC Errors result from ZBUG's calls to the BASIC ROM. The BASIC error code for these errors is stored at address START + 3 (where START is the start of ZBGASM).

#### BP BAD BREAKPOINT (ZBUG)

You are attempting to set a breakpoint (1) greater than 7, (2) in ROM, (3) at a SWI command, (4) at an address where one is already set.

BTO BYTE OVERFLOW (Assembler)

There is a field overflow in an 8-bit data quantity.

CMD COMMAND ERROR (ZBUG)

You are not using a ZBUG command.

CON CAN'T CONTINUE (ZBUG)