# **Technical Manual**

Appendices Z-100 Series Computers

593-0052-02 CONSISTS OF

MANUAL 595-2960-02

FLYSHEET 597-2922-02

TAB SET 597-2931

TM-100

### **RESTRICTED RIGHTS LEGEND**

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in paragraph (b)(3)(B) of the Rights in Technical Data and Computer Software clause in DAR 7-104.9(a). Contractor/Manufacturer is Zenith Data Systems Corporation of Hilltop Road, St. Joseph, Michigan 49085.

Copyright © 1983 by Zenith Data Systems Corporation, all rights reserved.

Printed in the United States of America.

Zenith Data Systems Corporation Saint Joseph, Michigan 49085

# This Document was scanned and contributed by:

# Barry A. Watzman

### TABLE OF CONTENTS

## Appendices

| Appendix A | S-100 Bus A.1                         |

|------------|---------------------------------------|

| Appendix B | 8085 Architecture B.1                 |

| Appendix C | 8085 Instruction Set C.1              |

| Appendix D | iAPX88 Book and Other Data Sheets D.1 |

IV

### Description

In Appendix A, you are furnished with the IEEE Task 696.1/D2, S-100 Bus Standards.

In Appendices B and C, you are furnished the architecture and instruction sets for the Intel 8085 microprocessor.

The 8085 microprocessor is an 8-bit general purpose microprocessor that is capable of accessing up to 64K bytes of memory and has status lines for controlling large systems.

Contained in the 8085 microprocessor are the functions of clock generation, system bus control, and interrupt priority selection, in addition to execution of the instruction set.

The 8085 microprocessor implements a group of instructions that move data between registers, between a register and memory, and between a register and an I/O port. It also has arithmetic and logic instructions, and machine control instruction. The CPU recognizes these instructions only when they are coded in binary form.

The architecture and instruction set for the 8088 microprocessor are located in the iAPX 88 Book, which is included as part of this Appendix.

The 8088 microprocessor is an 8-bit microprocessor. It combines a 16-bit microprocessor internal architecture with an easy to use 8-bit bus interface. Most of the bus lines are identical in function to the 8085A.

The 8088 is totally software compatable with the 16-bit 8086 CPU. All the power of the 8086 16-bit instruction set is available in the 8-bit 8088.

With the 16-bit internal architecture, the 8088 provides 16-bit wide registers, data paths, a 16-bit ALU, and a set of powerful 16-bit instructions identical to the ones found in the 8086 microprocessor. It also provides a 20-bit memory address range and a 16-bit input/output port address range for I/O cycles. This gives the 8088 a full megabyte of memory address sability and 64K bytes of I/O addressability.

The instruction set for the 8088 includes a full complement of arithmetic operations including addition, subtraction, multiplication, and division, on 8-bit or 16-bit quantities. If also has a complete set of string manipulation operations for performance and flexibility in application where large amounts of data are involved.

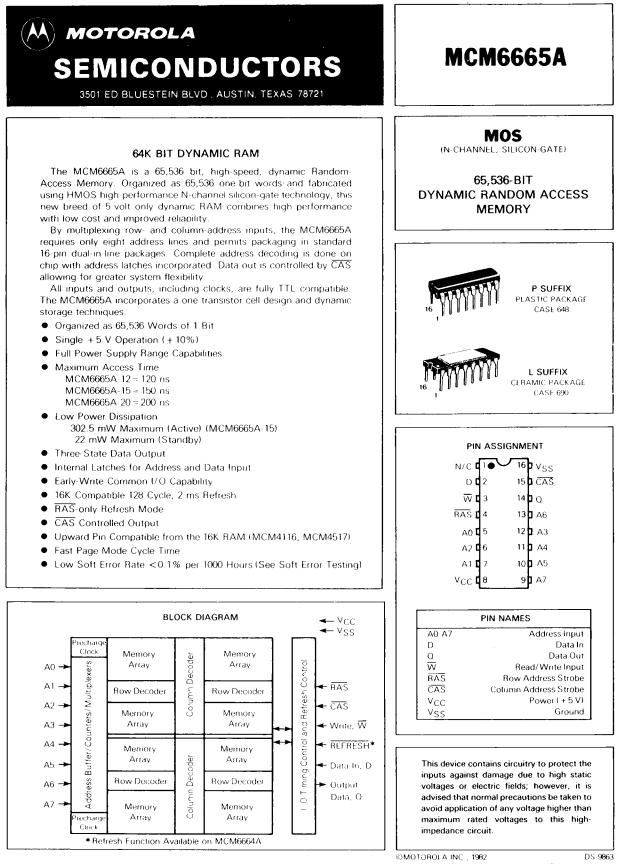

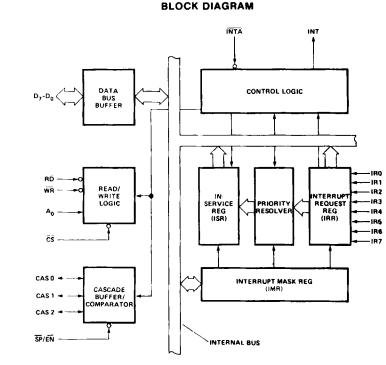

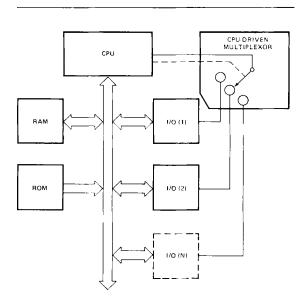

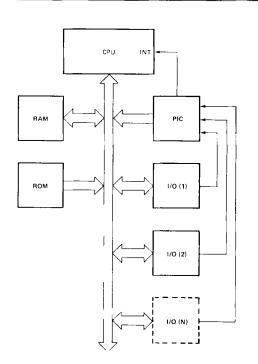

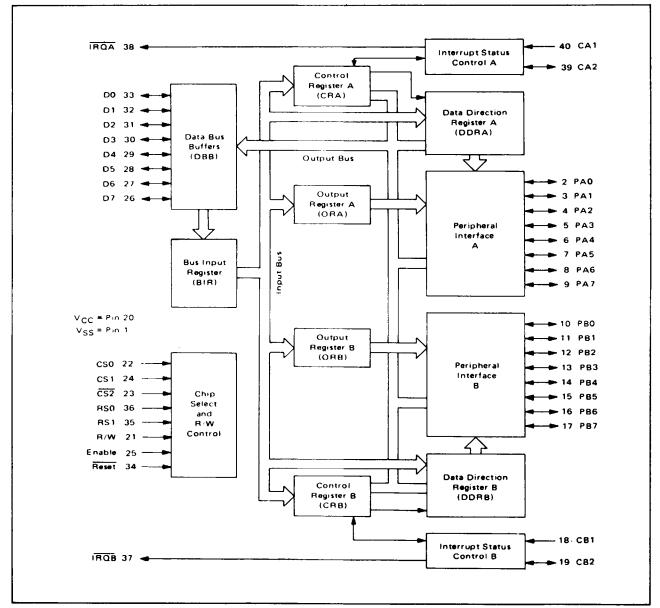

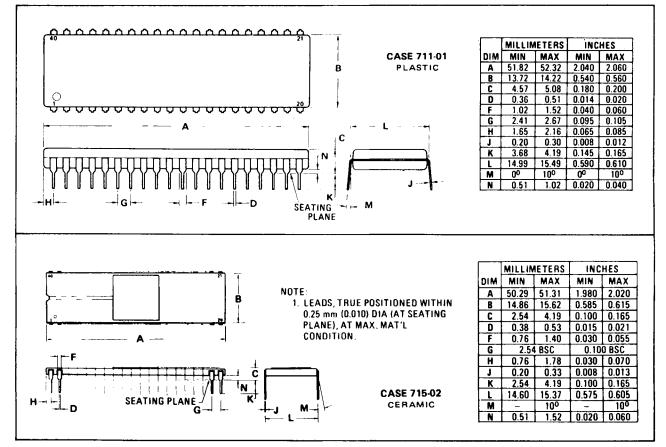

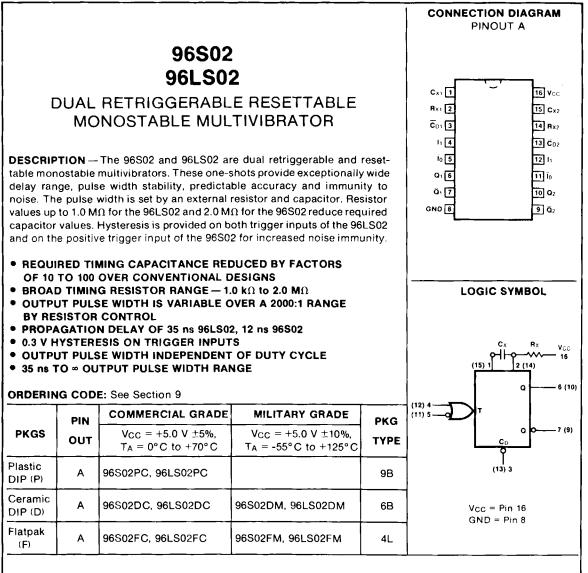

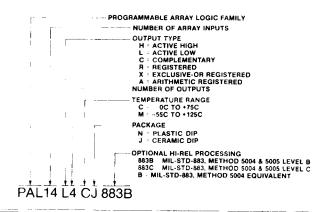

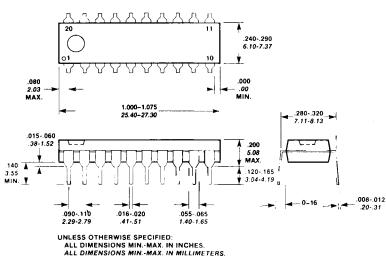

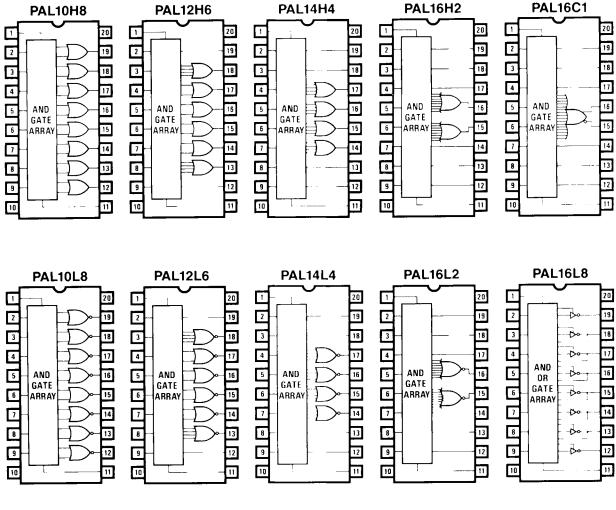

Appendix D provides you with the data sheets and programming instruction for the major IC's.

### APPENDIX A

### S100 Bus Specifications

The following pages provide you 1EEE Task 696.1/D2, S-100 Bus Standards.

### APPENDIX B 8085 Architecture

The following pages are reprinted with the permission of Intel Corporation.

### **8085A ARCHITECTURE**

### 2.1 WHAT THE 8085A IS

The 8085A is an 8-bit general-purpose microprocessor that is very cost-effective in small systems because of its extraordinarily low hardware overhead requirements. At the same time it is capable of accessing up to 64K bytes of memory and has status lines for controlling large systems.

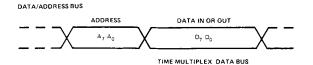

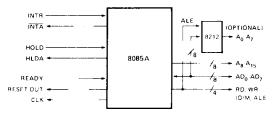

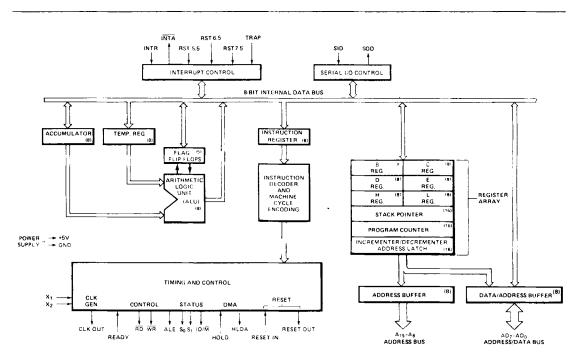

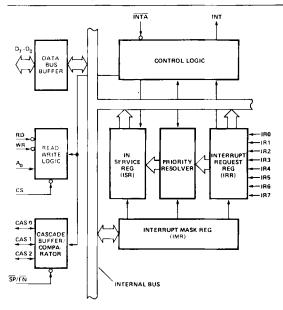

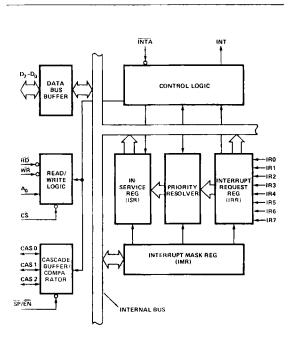

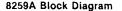

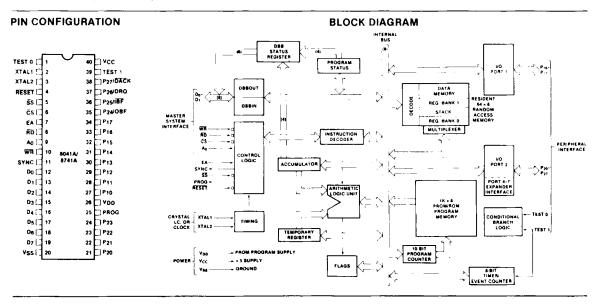

#### 2.2 WHAT'S IN THE 8085A

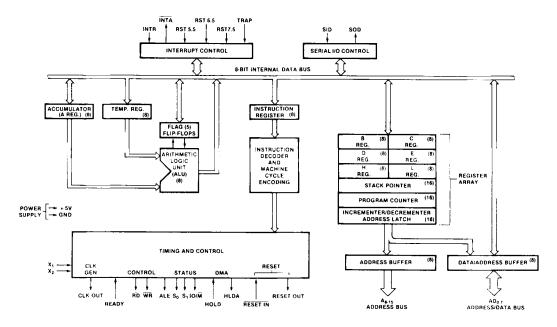

In the 8085A microprocessor are contained the functions of clock generation, system bus control, and interrupt priority selection, in addition to execution of the instruction set. (See Figure 2-1.) The 8085A transfers data on an 8-bit, bidirectional 3-state bus  $(AD_{0.7})$  which is time-multiplexed so as to also transmit the eight lower-order address bits. An additional eight lines  $(A_{8-15})$  expand the MCS-85 system memory addressing capability to 16 bits, thereby allowing 64K bytes of memory to be accessed directly by the CPU. The 8085A CPU (central processing unit) generates control signals that can be used to select appropriate external devices and

functions to perform READ and WRITE operations and also to select memory or I/O ports. The 8085A can address up to 256 different I/O locations. These addresses have the same numerical values (00 through FFH) as the first 256 memory addresses; they are distinguished by means of the IO/M output from the CPU. You may also choose to address I/O ports as memory locations (i.e., memory-map the I/O, Section 3.2).

#### 2.2.1 Registers

The 8085A, like the 8080, is provided with internal 8-bit registers and 16-bit registers. The 8085A has eight addressable 8-bit registers. Six of them can be used either as 8-bit registers or as 16-bit register pairs. Register pairs are treated as though they were single, 16-bit registers; the high-order byte of a pair is located in the first register and the low-order byte is located in the second. In addition to the register pairs, the 8085A contains two more 16-bit registers.

FIGURE 2-1 8085A CPU FUNCTIONAL BLOCK DIAGRAM

The 8085A's CPU registers are distinguished as follows:

- The accumulator (ACC or A Register) is the focus of all of the accumulator instructions (Table 4-1), which include arithmetic, logic, load and store, and I/O instructions. It is an 8-bit register only. (However, see Flags, in this list.)

- The program counter (PC) always points to the memory location of the next instruction to be executed. It always contains a 16-bit address.

- General-purpose registers BC, DE, and HL may be used as six 8-bit registers or as three 16-bit registers, interchangeably, depending on the instruction being performed. HL functions as a data pointer to reference memory addresses that are either the sources or the destinations in a number of instructions. A smaller number of instructions can use BC or DE for indirect addressing.

- The stack pointer (SP) is a special data pointer that always points to the stack top (next available stack address). It is an indivisible 16-bit register.

- The **flag register** contains five one-bit flags, each of which records processor status information and may also control processor operation. (See following paragraph.)

#### 2.2.2 Flags

The five flags in the 8085A CPU are shown below:

| D <sub>7</sub> | D <sub>6</sub> | $D_5$ | D₄ | $D_3$ | D <sub>2</sub> | D1 | $D_0$ |

|----------------|----------------|-------|----|-------|----------------|----|-------|

| S              | Z              |       | AC |       | Ρ              |    | СҮ    |

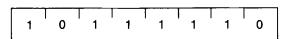

The **carry flag** (CY) is set and reset by arithmetic operations. Its status can be directly tested by a program. For example, the addition of two one-byte numbers can produce an answer that does not fit into one byte:

| HEXIDECIMAL  |        |   |   | BI | NA | RY |   |   |   |

|--------------|--------|---|---|----|----|----|---|---|---|

| AEH          |        | 1 | 0 | 1  | 0  | 1  | 1 | 1 | 0 |

| <u>+ 74H</u> | _      | 0 | 1 | 1  | 1  | 0  | 1 | 0 | 0 |

| 122H         | 1<br>† | 0 | 0 | 1  | 0  | 0  | 0 | 1 | 0 |

Carry bit sets carry flag to 1

An addition operation that results in an overflow out of the high-order bit of the accumulator sets the carry flag. An addition operation that does not result in an overflow clears the carry flag. (See 8080/8085 Assembly Language Programming Manual for further details.) The carry flag also acts as a "borrow" flag for subtract operations.

The **auxiliary carry flag** (AC) indicates overflow out of bit 3 of the accumulator in the same way that the carry flag indicates overflow out of bit 7. This flag is commonly used in BCD (binary coded decimal) arithmetic.

The **sign flag** is set to the condition of the most significant bit of the accumulator following the execution of arithmetic or logic instructions. These instructions use bit 7 of data to represent the sign of the number contained in the accumulator. This permits the manipulation of numbers in the range from -128 to +127.

The **zero flag** is set if the result generated by certain instructions is zero. The zero flag is cleared if the result is not zero. A result that has a carry but has a zero answer byte in the accumulator will set both the carry flag and the zero flag. For example,

| HEXADECIMAL  |         |     | I | BII  | NA  | R, | Y   |     |            |

|--------------|---------|-----|---|------|-----|----|-----|-----|------------|

| A7H          |         | 1   | 0 | 1    | 0   | 0  | 1   | 1   | 1          |

| <u>+ 59H</u> |         | 0   |   |      |     |    |     |     |            |

| 100H         | أسر     | ٥   | 0 | 0    | 0   | 0  | 0   | 0   | 0          |

|              | Carry I | bit |   |      | 1   |    |     |     |            |

| Link         | hi      |     |   | ۰- I | ~ * |    | 104 | ~ * | <u>~ 1</u> |

Eight zero bits set zero flag to 1

Incrementing or decrementing certain CPU registers with a zero result will also set the zero flag.

The **parity flag** (P) is set to 1 if the parity (number of 1-bits) of the accumulator is even. If odd, it is cleared.

#### 2.2.3 Stack

The stack pointer maintains the address of the last byte entered into the stack. The stack pointer can be initialized to use any portion of read-write memory as a stack. The stack pointer is decremented each time data is pushed onto the stack and is incremented each time data is popped off the stack (i.e., the stack grows downward in terms of memory address, and the stack "top" is the lowest numerical address represented in the stack currently in use). Note that the stack pointer is always incremented or decremented by two bytes since all stack operations apply to register pairs.

.- - .

### 2.2.4 Arithmetic-Logic Unit (ALU)

The ALU contains the accumulator and the flag register (described in Sections 2.2.1 and 2.2.2) and some temporary registers that are inaccessible to the programmer.

Arithmetic, logic, and rotate operations are performed by the ALU. The results of these operations can be deposited in the accumulator, or they can be transferred to the internal data bus for use elsewhere.

#### 2.2.5 Instruction Register and Decoder

During an instruction fetch, the first byte of an instruction (containing the opcode) is transferred from the internal bus to the 8-bit instruction register. (See Figure 2-1.) The contents of the instruction register are, in turn, available to the instruction decoder. The output of the decoder, gated by timing signals, controls the registers, ALU, and data and address buffers. The outputs of the instruction decoder and internal clock generator generate the state and machine cycle timing signals.

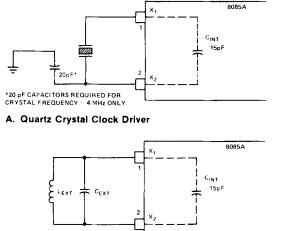

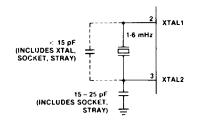

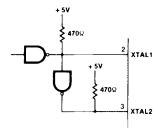

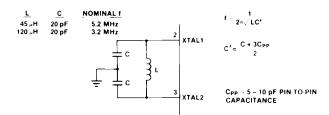

### 2.2.6 Internal Clock Generator

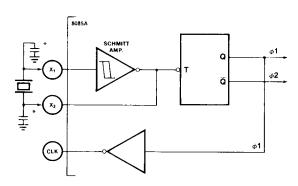

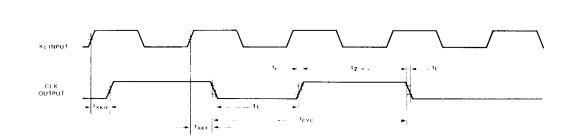

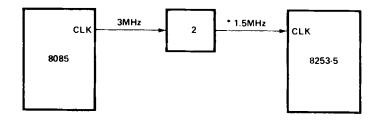

The 8085A CPU incorporates a complete clock generator on its chip, so it requires only the addition of a quartz crystal to establish timing for its operation. (It will accept an external clock input at its  $X_1$  input instead, however.) A suitable crystal for the standard 8085A must be parallel-resonant at a fundamental of 6.25 MHz or less, twice the desired internal clock frequency. The 8085A-2 will operate with crystal of up to 10 MHz. The functions of the 8085A internal clock generator are shown in Figure 2-2. A Schmitt trigger is used interchangeably as oscillator or

\*EXTERNAL CAPACITORS REQUIRED ONLY FOR CRYSTAL FREQUENCIES : 4MHz.

FIGURE 2-2 8085A CLOCK LOGIC

as input conditioner, depending upon whether a crystal or an external source is used. The clock circuitry generates two nonoverlapping internal clock signals,  $\phi_1$  and  $\phi_2$  (see Figure 2-2).  $\phi_1$  and  $\phi_2$  control the internal timing of the 8085A and are not directly available on the outside of the chip. The external pin CLK is a buffered, inverted version of  $\phi_1$ . CLK is half the frequency of the crystal input signal and may be used for clocking other devices in the system.

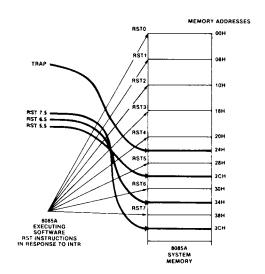

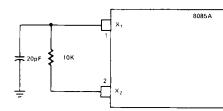

FIGURE 2-3 8085A HARDWARE AND SOFT-WARE RST BRANCH LOCATIONS

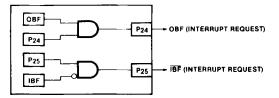

#### 2.2.7 Interrupts

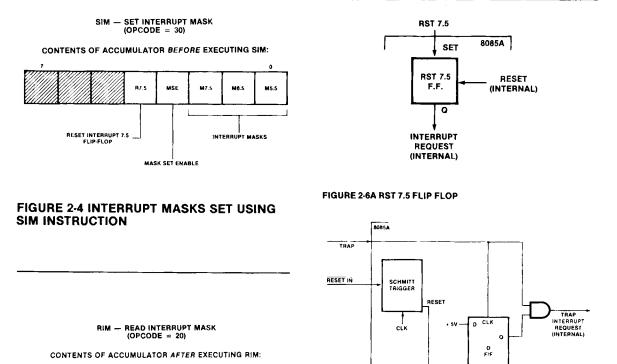

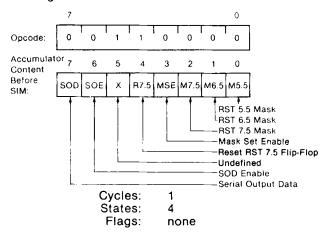

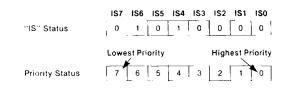

The five hardware interrupt inputs provided in the 8085A are of three types. INTR is identical with the 8080A INT line in function; i.e., it is maskable (can be enabled or disabled by El or DI software instructions), and causes the CPU to fetch in an RST instruction, externally placed on the data bus, which vectors a branch to any one of eight fixed memory locations (Restart addresses). (See Figure 2-3.) INTR can also be controlled by the 8259 programmable interrupt controller, which generates CALL instructions instead of RSTs, and can thus vector operation of the CPU to a preprogrammed subroutine located anywhere in your system's memory map. The RST 5.5, RST 6.5, and RST 7.5 hardware interrupts are different in function in that they are maskable through the use of the SIM

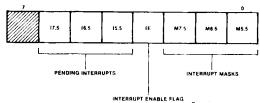

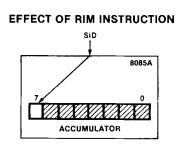

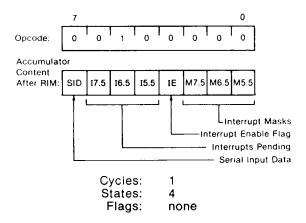

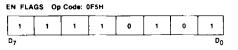

instruction, which enables or disables these interrupts by clearing or setting corresponding mask flags based on data in the accumulator. (See Figure 2-4.) You may read the status of the interrupt mask previously set by peforming a RIM instruction. Its execution loads into the accumulator the following information. (See Figure 2-5.)

- Current interrupt mask status for the RST 5.5, 6.5, and 7.5 hardware status.

- Current interrupt enable flag status (except that immediately following TRAP, the IE flag status preceding that interrupt is loaded).

- RST 5.5, 6.5, and 7.5 interrupts pending.

RST 5.5, 6.5, and 7.5 are also subject to being enabled or disabled by the EI and DI instructions, respectively. INTR, RST 5.5, and RST 6.5 are level-sensitive, meaning that these inputs may be acknowledged by the processor when they are held at a high level. RST 7.5 is edgesensitive, meaning that an internal flip-flop in the 8085A registers the occurrence of an interrupt the instant a rising edge appears on the RST 7.5 input line. This input need not be held high; the flip-flop will remain set until it is cleared by one of three possible actions:

• The 8085A responds to the interrupt, and sends an internal reset signal to the RST 7.5 flip-flop. (See Figure 2-6A.)

FIGURE 2-5 RIM - READ INTERRUPT MASK

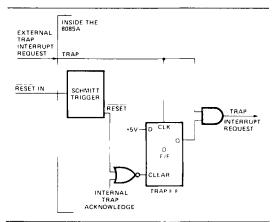

### FIGURE 2-6 RST 7.5 AND TRAP INTERRUPT INPUTS

INTERNAL TRAP ACKNOWLEDGE

**FIGURE 2-6B TRAP INTERRUPT INPUTS**

TRAPEE

- The 8085A, before responding to the RST 7.5 interrupt, receives a RESET IN signal from an external source; this also activates the internal reset.

- The 8085A executes a SIM instruction, with accumulator bit 4 previously set to 1. (See Figure 2-4.)

The third type of hardware interrupt is TRAP. This input is not subject to any mask or interrupt enable/disable instruction. The receipt of a positive-going edge on the TRAP input triggers the processor's hardware interrupt sequence, but the pulse must be held high until acknowledged internally (see Figure 2-6B).

The sampling of all interrupts occurs on the descending edge of CLK, one cycle before the end of the instruction in which the interrupt input is activated. To be recognized, a valid interrupt must occur at least 160 ns before sampling time in the 8085A, or 150 ns in the 8085A-2. This means that to guarantee being recognized, RST 5.5 and 6.5 and TRAP need to be held on for at least 17 clock states plus 160 ns (150 for 8085A-2), assuming that the interrupt might arrive just barely too late to be acknowledged during a particular instruction, and that the following instruction might be an 18-state CALL. This timing assumes no WAIT or HOLD cycles are used.

The way interrupt masks are set and read is described in Chapter 4 under the RIM (read in-

terrupt mask) and SIM (set interrupt mask) instruction listings. Interrupt functions and their priorities are shown in the table that follows.

| Name    | Priority | Address (1)<br>Branched to<br>when inter-<br>rupt occurs | Type<br>Trigger                                   |

|---------|----------|----------------------------------------------------------|---------------------------------------------------|

| TRAP    | 1        | 24H                                                      | Rising edge<br>AND high<br>level until<br>sampled |

| RST 7.5 | 2        | 3CH                                                      | Rising edge<br>(latched)                          |

| RST 6.5 | 3        | 34H                                                      | High level<br>until sam-<br>pled                  |

| RST 5.5 | 4        | 2CH                                                      | High level<br>until sam-<br>pled                  |

| INTR    | 5        | (2)                                                      | High level<br>until sam-<br>pled                  |

NOTES:

- (1) In the case of TRAP and RST 5.5-7.5, the contents of the Program Counter are pushed onto the stack before the branch occurs.

- (2) Depends on the instruction that is provided to the 8085A by the 8259 or other circuitry when the interrupt is acknowledged.

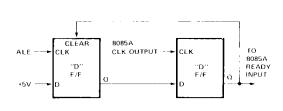

#### 2.2.8 Serial Input and Output

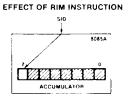

The SID and SOD pins help to minimize chip count in small systems by providing for easy interface to a serial port using software for timing and for coding and decoding of the data. Each time a RIM instruction is executed, the status of the SID pin is read into bit 7 of the accumulator. RIM is thus a dual-purpose instruction. (See Chapter 4.) In similar fashion, SIM is used to latch bit 7 of the accumulator out to the SOD output via an internal flip-flop, providing that bit 6 of the accumulator is set to 1. (See Figure 2-7.) Section 2.3.8 describes SID and SOD timing.

SID can also be used as a general purpose TEST input and SOD can serve as a one-bit control output.

EFFECT OF SIM INSTRUCTION

### FIGURE 2-7 EFFECT OF RIM AND SIM INSTRUCTIONS ON SERIAL DATA LINES

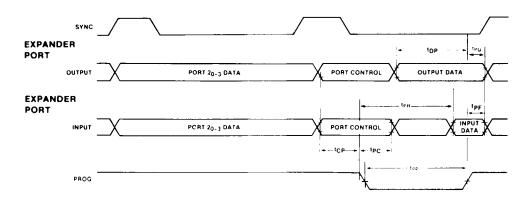

### 2.3 HOW THE MCS-85 SYSTEM WORKS

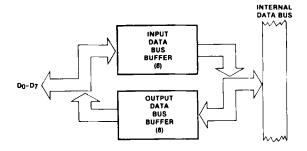

The 8085A CPU generates signals that tell peripheral devices what type of information is on the multiplexed Address/Data bus and from that point on the operation is almost identical to the MCS-80<sup>TM</sup> CPU Group. A multiplexed bus structure was chosen because it freed device pins so that more functions could be integrated on the 8085A and other components of the family. The multiplexed bus is designed to allow complete compatibility to existing peripheral

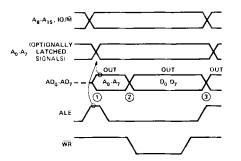

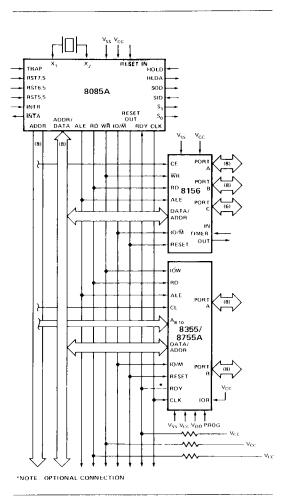

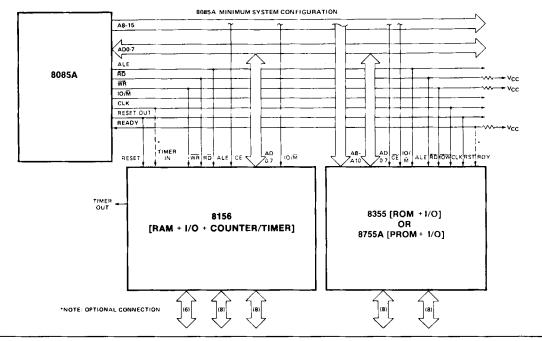

components with improved timing margins and access requirements. (See Figure 2-8.)

To enhance the system integration of MCS-85, several special components with combined memory and I/O were designed. These new devices directly interface to the multiplexed bus of the 8085A. The pin locations of the 8085A and the special peripheral components are assigned to minimize PC board area and to allow for efficient layout. The details on peripheral components are contained in subsequent paragraphs of this chapter and in Chapters 5 and 6.

8085A

ADDRESS BUS

MULTIPLEXED ADDRESS/DATA BUS

ALE

ŔD

WR IO/M

FIGURE 2-8A MCS-80™ CPU GROUP

FIGURE 2-8B MCS-85<sup>TM</sup> CPU/8085A (MCS-80 COMPATIBLE FUNCTIONS)

FIGURE 2-8C MULTIPLEXED BUS TIMING

FIGURE 2-8 BASIC CPU FUNCTIONS

### 2.3.1 Multiplexed Bus Cycle Timing

The execution of any 8085A program consists of a sequence of READ and WRITE operations, of which each transfers a byte of data between the 8085A and a particular memory or I/O address. These READ and WRITE operations are the only communication between the processor and the other components, and are all that is necessary to execute any instruction or program.

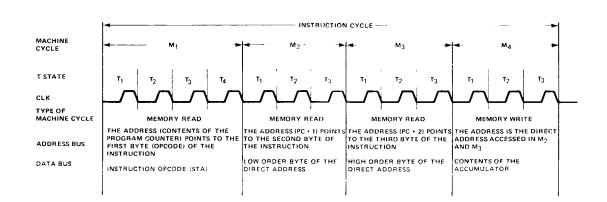

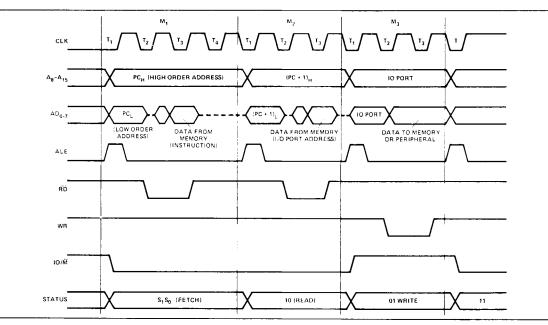

Each READ or WRITE operation of the 8085A is referred to as a machine cycle. The execution of each instruction by the 8085A consists of a seguence of from one to five machine cycles, and each machine cycle consists of a minimum of from three to six clock cycles (also referred to as T states). Consider the case of the Store Accumulator Direct (STA) instruction, shown in Figure 2-9. The STA instruction causes the contents of the accumulator to be stored at the direct address specified in the second and third bytes of the instruction. During the first machine cycle (M1), the CPU puts the contents of the program counter (PC) on the address bus and performs a MEMORY READ cycle to read from memory the opcode of the next instruction (STA). The M<sub>1</sub> machine cycle is also referred to as the OPCODE FETCH cycle, since it fetches the operation code of the next instruction. In the fourth clock cycle (T<sub>4</sub>) of M<sub>1</sub>, the CPU interprets the data read in and recognizes it as the opcode of the STA instruction. At this point the CPU knows that it must do three more machine cycles (two MEMORY READs and one MEMORY WRITE) to complete the instruction.

The 8085A then increments the program counter so that it points to the next byte of the instruction and performs a MEMORY READ machine cycle (M<sub>2</sub>) at address (PC + 1). The accessed memory places the addressed data on the data bus for the CPU. The 8085A temporarily stores this data (which is the low-order byte of the direct address) internally in the CPU. The 8085A again increments the program counter to location (PC + 2) and reads from memory (M<sub>3</sub>) the next byte of data, which is the highorder byte of the direct address.

At this point, the 8085A has accessed all three bytes of the STA instruction, which it must now execute. The execution consists of placing the data accessed in  $M_2$  and  $M_3$  on the address bus, then placing the contents of the accumulator on the data bus, and then performing a MEMORY WRITE machine cycle ( $M_4$ ). When  $M_4$ is finished, the CPU will fetch ( $M_1$ ) the first byte of the next instruction and continue from there.

#### **State Transition Sequence**

As the preceding example shows, the execution of an instruction consists of a series of machine cycles whose nature and sequence is determined by the opcode accessed in the  $M_1$

FIGURE 2-9 CPU TIMING FOR STORE ACCUMULATOR DIRECT (STA) INSTRUCTION

| MACHINE CYCLE    |       |                 |   | STAT | US |    | CON   | TROL |      |

|------------------|-------|-----------------|---|------|----|----|-------|------|------|

| MACHINE GYCLE    |       | [               | Γ | IO/M | S1 | SO | RD    | WŔ   | ÎNT/ |

| OPCODE FETCH     | (OF)  |                 |   | 0    | 1  | 1  | 0     | 1    | 1    |

| MEMORY READ      | (MR)  |                 |   | 0    | 1  | 0  | 0     | 1    | 1    |

| MEMORY WRITE     | (MW)  |                 |   | 0    | 0  | 1  | 1     | 0    | t    |

| I/O READ         | (IOR) |                 |   | 1    | 1  | 0  | 0     | 1    | 1    |

| I/O WRITE        | (IOW) |                 |   | 1    | 0  | 1  | 1     | 0    | 1    |

| INTR ACKNOWLEDGE | (INA) |                 |   | 1    | 1  | 1  | 1     | 1    | 0    |

| BUSIDLE          | (B1). | DAD             |   | 0    | 1  | 0  | 1     | 1    | 1    |

|                  |       | INA(RST/TRAP) i | i | 1    | 1  | t  | ( t., | 1.1  | 1    |

|                  |       | HALT            |   | ΥS.  | 0  | 0  | TS    | TS   | t    |

#### FIGURE 2-10 8085A MACHINE CYCLE CHART

machine cycle. While no one instruction cycle will consist of more than five machine cycles, every machine cycle will be one of the seven types listed in Figure 2-10. These seven types of machine cycles can be differentiated by the state of the three status lines ( $IO/\overline{M}$ ,  $S_0$ , and  $S_1$ ) and the three control signals ( $\overline{RD}$ ,  $\overline{WR}$ , and  $\overline{INTA}$ ).

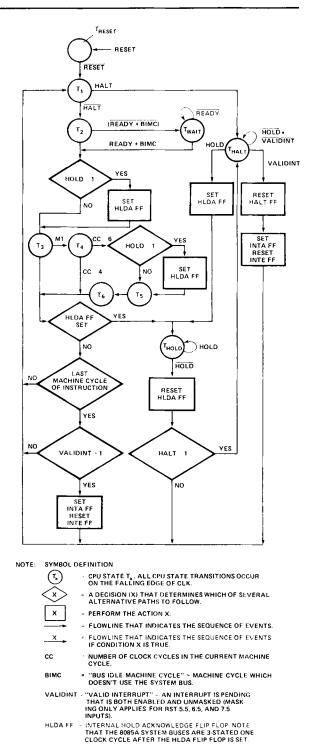

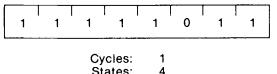

Most machine cycles consist of three T states, (cycles of the CLK output) with the exception of OPCODE FETCH, which normally has either four or six T states. The actual number of states required to perform any instruction depends on the instruction being executed, the particular machine cycle within the instruction cycle, and the number of WAIT and HOLD states inserted into each machine cycle through the use of the READY and HOLD inputs of the 8085A. The state transition diagram in Figure 2-11 illustrates how the 8085A proceeds in the course of a machine cycle. The state of various status and control signals, as well as the system buses, is shown in Figure 2-12 for each of the ten possible T states that the processor can be in.

Figure 2-11 also shows when the READY, HOLD, and interrupt signals are sampled, and how they modify the basic instruction sequence ( $T_1$ - $T_6$  and  $T_{WAIT}$ ). As we shall see, the timings for each of the seven types of machine cycles are almost identical.

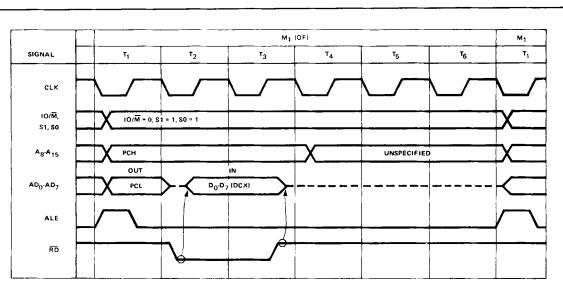

### **OPCODE FETCH (OF):**

The OPCODE FETCH (OF) machine cycle is unique in that it has more than three clock cycles. This is because the CPU must interpret the opcode accessed in  $T_1$ ,  $T_2$ , and  $T_3$  before it can decide what to do next.

FIGURE 2-11 8085A CPU STATE TRANSITION

|                  | [     | Stat | us & Bu | ses     | C  | ontrol | <u>ار</u> |  |

|------------------|-------|------|---------|---------|----|--------|-----------|--|

| Machine<br>State | S1,S0 | 10/M | A8-A15  | AD0-AD7 |    | INTA   | ALE       |  |

| Т1               | x     | X    | х       | х       | 1  | 1      | 11        |  |

| Т2               | х     | х    | x       | ×       | х  | х      | 0         |  |

| TWAIT            | х     | x    | x       | x       | x  | х      | 0         |  |

| Т3               | х     | ' x  | ×       | ×       | Х  | х      | 0         |  |

| Τ4               | 1     | 0'   | ×       | TS      | 1  | 1      | 0         |  |

| Т5               | 1     | 0.   | x       | TS      | 1  | 1      | 0         |  |

| т <sub>6</sub>   | 1     | 0*   | ×       | TS      | 1  | 1      | 0         |  |

| TRESET           | х     | тs   | TS      | ΤS      | TS | 1      | 0         |  |

| THALT            | 0     | тs   | тs      | TS      | ΤS | 1      | 0         |  |

| THOLD            | х     | TS   | TS      | тs      | тs | . 1    | 0         |  |

$0 = \text{Logic "0"} \quad 1 = \text{Logic "1"} \quad TS = \text{High Impedance} \quad X = \text{Unspecified} \\ ^{\dagger}\text{ALE not generated during 2nd and 3rd machine cycles of DAD}$

instruction.

\*IO/ $\overline{M}$  = 1 during T<sub>4</sub>-T<sub>6</sub> states of RST and INA cycles.

### FIGURE 2-12 8085A MACHINE STATE CHART

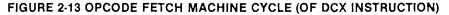

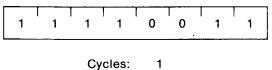

Figure 2-13 shows the timing relationships for an OF machine cycle. The particular instruction illustrated is DCX, whose timing for OF differs from other instructions in that it has six T states, while some instructions require only four T states for OF. In this discussion, as well as the following discussions, only the relative timing of the signals will be discussed; for the actual timings, refer to the data sheets of the individual parts in Chapters 5 and 6.

The first thing that the 8085A does at the beginning of every machine cycle is to send out three status signals (IO/M, S1, S0) that define what type of machine cycle is about to take place. The IO/M signal identifies the machine cycle as being either a memory reference or input/output operation. The S1 status signal identifies whether the cycle is a READ or WRITE operation. The S0 and S1 status signals can be used together (see Figure 2-10) to identify READ, WRITE, or OPCODE FETCH machine cycles as well as the HALT state. Referring to Figure 2-13, the 8085A will send out  $IO/\overline{M} = 0$ , S1 = 1, S0 = 1at the beginning of the machine cycle to identify it as a READ from a memory location to obtain an opcode; in other words, it identifies the machine cycle as an OPCODE FETCH cycle.

The 8085A also sends out a 16-bit address at the beginning of every machine cycle to identify the particular memory location or I/O port that the machine cycle applies to. In the case of an OF cycle, the contents of the program counter is placed on the address bus. The high order byte (PCH) is placed on the A8-A15 lines, where it will stay until at least T<sub>4</sub>. The low order byte (PCL) is placed on the AD<sub>0</sub>-AD<sub>7</sub> lines, whose three-state drivers are enabled if not found already on. Unlike the upper address lines, however, the information on the lower address lines will remain there for only one clock cycle, after which the drivers will go to their high impedance state, indicated by a dashed line in Figure 2-13. This is necessary because the AD<sub>0</sub>-AD<sub>7</sub> lines are time mulitplexed between the address and data buses. During T<sub>1</sub> of every machine cycle, AD<sub>0</sub>-AD7 output the lower 8-bits of address after which AD<sub>0</sub>-AD<sub>7</sub> will either output the desired data for a WRITE operation or the drivers will float (as is the case for the OF cycle), allowing the external device to drive the lines for a READ operation.

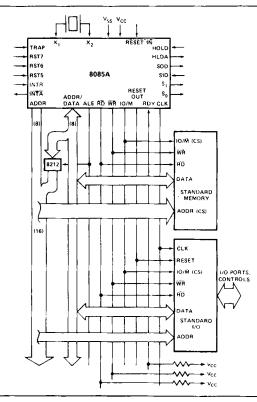

Since the address information on  $AD_0$ - $AD_7$  is of a transitory nature, it must be latched either internally in special multiplexed-bus components like the 8155 or externally in parts like the 8212 8-bit latch. (See Chapter 3.) The 8085A provides a special timing signal, ADDRESS LATCH ENABLE (ALE), to facilitate the latching of A<sub>0</sub>-A<sub>7</sub>; ALE is present during T<sub>1</sub> of every machine cycle.

After the status signals and address have been sent out and the AD0-AD7 drivers have been disabled, the 8085A provides a low level on RD to enable the addressed memory device. The device will then start driving the AD<sub>0</sub>-AD<sub>7</sub> lines; this is indicated by the dashed line turning into a solid line in Figure 2-13. After a period of time (which is the access time of the memory) valid data will be present on AD<sub>0</sub>-AD<sub>7</sub>. The 8085A during T<sub>3</sub> will load the memory data on AD<sub>0</sub>-AD<sub>7</sub> into its instruction register and then raise RD to the high level, disabling the addressed memory device. At this point, the 8085A will have finished accessing the opcode of the instruction. Since this is the first machine cycle (M1) of the instruction, the CPU will automatically step to  $T_4$ , as shown in Figure 2-11.

During  $T_4$ , the CPU will decode the opcode in the instruction register and decide whether to enter  $T_5$  on the next clock or to start a new machine cycle and enter  $T_1$ . In the case of the DCX instruction shown in Figure 2-13, it will enter  $T_5$  and then  $T_6$  before going to  $T_1$ .

During  $T_5$  and  $T_6$ , of DCX, the CPU will decrement the designated register. Since the A8-A15 lines are driven by the address latch circuits, which are part of the incrementer/decrementer logic, the  $A_8$ - $A_{15}$  lines may change during  $T_5$  and T<sub>6</sub>. Because the value of A<sub>8</sub>-A<sub>15</sub> can vary during T<sub>4</sub>-T<sub>6</sub>, it is most important that all memory and I/O devices on the system bus qualify their selection with  $\overline{RD}$ . If they don't use  $\overline{RD}$ , they may be spuriously selected. Moreover, with a linear selection technique (Chapter 3), two or more devices could be simultaneously enabled, which could be potentially damaging. The generation of spurious addresses can also occur momentarily at address bus transitional periods in  $T_1$ . Therefore, the selection of all memory and I/O devices must be qualified with RD or WR. Many new memory devices like the 8155 and 8355 have the RD input that internally is used to enable the data bus outputs, removing the need for externally qualifying the chip enable input with RD.

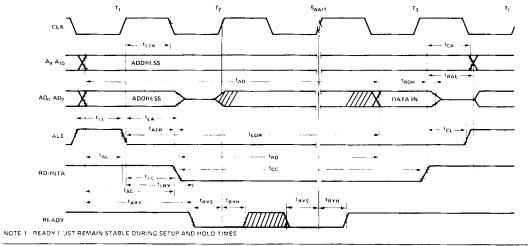

Figure 2-14 is identical to Figure 2-13 with one exception, which is the use of the READY line. As we can see in Figure 2-11, when the CPU is in  $T_2$ , it examines the state of the READY line. If the READY line is high, the CPU will proceed to  $T_3$  and finish executing the instruction. If the READY line is low, however, the CPU will enter  $T_{WAIT}$  and stay there indefinitely until READY goes high. When the READY line does go high, the CPU will exit  $T_{WAIT}$  and enter  $T_3$ , in order to complete the machine cycle. As shown in

Figure 2-14, the external effect of using the READY line is to preserve the exact state of the processor signals at the end of  $T_2$  for an integral number of clock periods, before finishing the machine cycle. This "stretching" of the system timing has the further effect of increasing the allowable access time for memory or I/O devices. By inserting  $T_{WAIT}$  states, the 8085A can accommodate even the slowest of memories. Another common use of the READY line is to singe-step the processor with a manual switch.

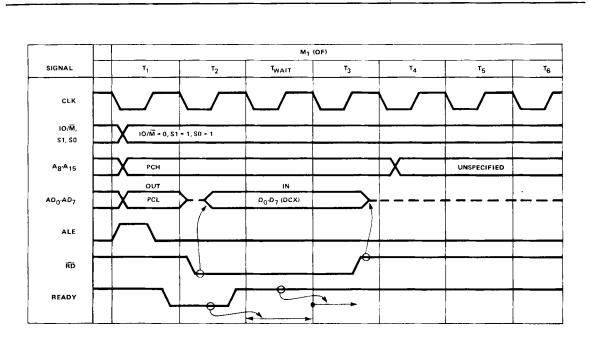

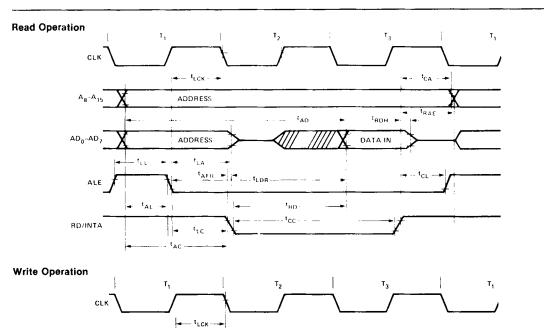

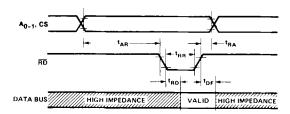

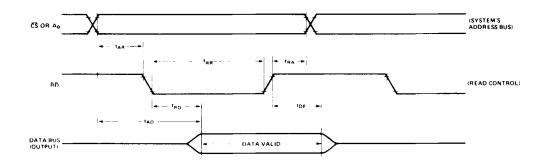

### 2.3.2 Read Cycle Timing MEMORY READ (MR):

Figure 2-15 shows the timing of two successive MEMORY READ (MR) machine cycles, the first without a  $T_{WAIT}$  state and the second with one  $T_{WAIT}$  state. The timing during  $T_1$ - $T_3$  is absolutely identical to the OPCODE FETCH machine cycle, with the exception that the status sent out during  $T_1$  is IO/ $\overline{M} = 0$ , S1 = 1, S0 = 0, identifying the cycles as a READ from a memory location. This differs from Figure 2-13 only in that S0 = 1 for an OF cycle, identifying that cycle as an OPCODE FETCH operation. Otherwise, the two cycles are identical during  $T_1$ - $T_3$ .

A second difference occurs at the end of  $T_3$ . As shown in Figure 2-11, the CPU always goes to  $T_4$ from  $T_3$  during  $M_1$ , which is always an OF cycle. During all other machine cycles, the CPU will always go from  $T_3$  to  $T_1$  of the next machine cycle.

**FUNCTIONAL DESCRIPTION**

### FIGURE 2-14 OPCODE FETCH MACHINE CYCLE WITH ONE WAIT STATE

### FIGURE 2-15 MEMORY READ (OR I/O READ) MACHINE CYCLES (WITH AND WITHOUT WAIT STATES)

The memory address used in the OF cycle is always the contents of the program counter, which points to the current instruction, while the address used in the MR cycle can have several possible origins. Also, the data read in during an MR cycle is placed in the appropriate register, not the instruction register.

### I/O READ (IOR):

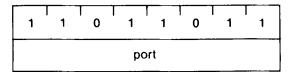

Figure 2-15 also shows the timing of two successive I/O READ (IOR) machine cycles, the first without a  $T_{WAIT}$  state. As is readily apparent, the timing of an IOR cycle is identical to the timing of an MR cycle, with the exception of  $IO/\overline{M} = 0$  for MR and  $IO/\overline{M} = 1$  for IOR; recall that  $IO/\overline{M}$  status signal identifies the address of the current machine cycle as selecting either a memory location or an I/O port. The address used in the IOR cycle comes from the second byte (Port No.) of an INPUT instruction. Note that the I/O port address is duplicated onto both AD<sub>0</sub>-AD<sub>7</sub> and A<sub>8</sub>-A<sub>15</sub>. The IOR cycle can occur only as the third machine cycle of an INPUT instruction.

Note that the READY signal can be used to generate  $T_{WAIT}$  states for I/O devices as well as memory devices. By gating the READY signal with the proper status lines, one could generate  $T_{WAIT}$  states for memory devices only or for I/O devices only. By gating in the address lines, one can further qualify  $T_{WAIT}$  state generation by the particular devices being accessed.

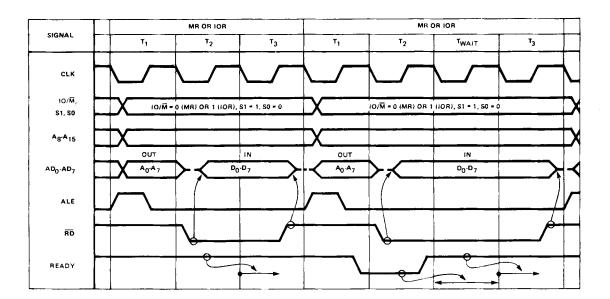

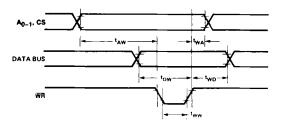

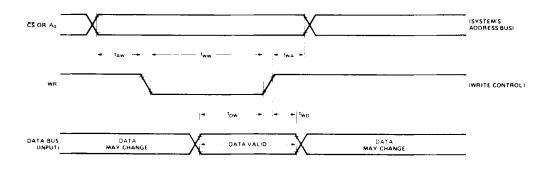

### 2.3.3 WRITE Cycle Timing MEMORY WRITE (MW):

Figure 2-16 shows the timing for two successive MEMORY WRITE (MW) machine cycles, the first without a  $T_{WAIT}$  state, and the second with one  $T_{WAIT}$  state. The 8085A sends out the status during  $T_1$  in a similar fashion to the OF, MR and IOR cycles, except that  $IO/\overline{M} = 0$ , S1 = 0, and S0 = 1, identifying the current machine cycle as being a WRITE operation to a memory location.

The address is sent out during  $T_1$  in an identical manner to MR. However, at the end of T<sub>1</sub>, there is a difference. While the AD<sub>0</sub>-AD<sub>7</sub> drivers were disabled during  $T_2$ - $T_3$  of MR in expectation of the addressed memory device driving the AD<sub>0</sub>-AD<sub>7</sub> lines, the drivers are not disabled for MW. This is because the CPU must provide the data to be written into the addressed memory location. The data is placed on AD<sub>0</sub>-AD<sub>7</sub> at the start of  $T_2$ . The  $\overline{WR}$  signal is also lowered at this time to enable the writing of the addressed memory device. During T<sub>2</sub>, the READY line is checked to see if a T<sub>WAIT</sub> state is required. If READY is low, TWAIT states are inserted until READY goes high. During  $T_3$ , the  $\overline{WR}$  line is raised, disabling the addressed memory device and thereby terminating the WRITE operation. The contents of the address and data lines are not changed until the next  $T_1$ , which directly follows.

Note that the data on  $AD_0$ - $AD_7$  is not guaranteed to be stable before the falling edge

FIGURE 2-16 MEMORY WRITE (OR I/O WRITE) MACHINE CYCLES (WITH AND WITHOUT WAIT STATES)

of  $\overline{\text{WR}}$ . The AD<sub>0</sub>-AD<sub>7</sub> lines are guaranteed to be stable both before and after the rising edge of  $\overline{\text{WR}}$ .

### I/O WRITE (IOW):

As Figure 2-16 shows, the timing for an I/O WRITE (IOW) machine cycle is the same as an MW machine cycle except that  $IO/\overline{M} = 0$  during the MW cycle and  $IO/\overline{M} = during$  the IOW cycle.

As with the IOR cycle discussed previously, the address used in an IOW cycle is the I/O port number which is duplicated on both the high and low bytes of the address bus. In the case of IOW, the port number comes from the second byte of an OUTPUT instruction as the instruction is executed.

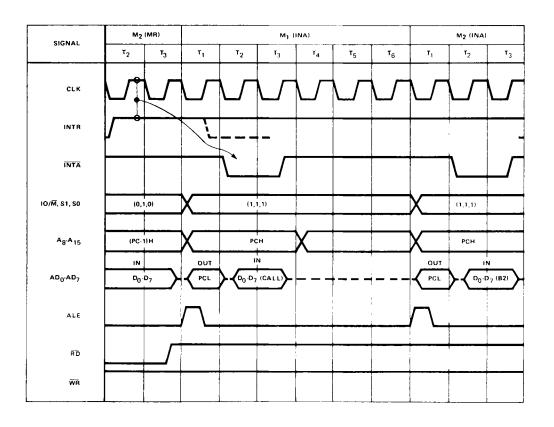

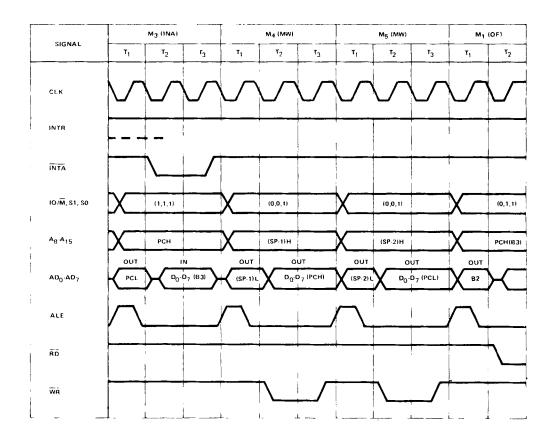

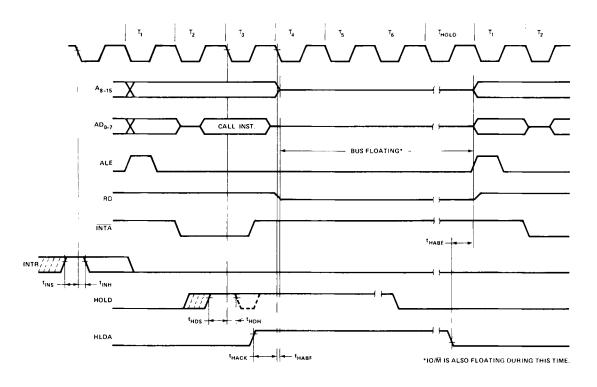

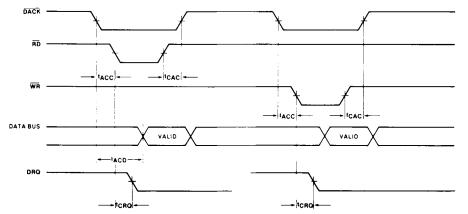

### 2.3.4 Interrupt Acknowledge (INA) Timing

Figures 2-17 and 2-18 (a continuation of 2-17) depict the course of action the CPU takes in response to a high level on the INTR line if the INTE FF (interrupt enable flip-flop) has been set

by the El instruction. The status of the TRAP and RST pins as well as INTR is sampled during the second clock cycle before  $M_1 \cdot T_1$ . If INTR was the only valid interrupt and if INTE FF is set, then the CPU will reset INTE FF and then enter an INTERRUPT ACKNOWLEDGE (INA) machine cycle. The INA cycle is identical to an OF cycle with two exceptions. INTA is sent out instead of RD. Also, IO/M = 1 during INA, whereas IO/M = 0 for OF. Although the contents of the program counter are sent out on the address lines, the address lines can be ignored.

When INTA is sent out, the external interrupt logic must provide the opcode of an instruction to execute. The opcode is placed on the data bus and read in by the processor. If the opcode is the first byte of a multiple-byte instruction, additional INTA pulses will be provided by the 8085A to clock in the remaining bytes. RESTART and CALL instructions are the most

FIGURE 2-17 INTERRUPT ACKNOWLEDGE MACHINE CYCLES (WITH CALL INSTRUCTION IN RESPONSE TO INTR)

logical choices, since they both force the processor to push the contents of the program counter onto the stack before jumping to a new location. In Figure 2-17 it is assumed that a CALL opcode is sent to the CPU during  $M_1$ . The CALL opcode could have been placed there by a device like the 8259 programmable interrupt controller.

After receiving the opcode, the processor then decodes it and determines, in this case, that the CALL instruction requires two more bytes. The CPU therefore performs a second INA cycle  $(M_2)$  to access the second byte of the instruction from the 8259. The timing of this cycle is identical to  $M_1$ , except that it has only three T states.  $M_2$  is followed by another INA cycle  $(M_3)$  to access the third byte of the CALL instruction from the 8259.

Now that the CPU has accessed the entire instruction used to acknowledge the interrupt, it will execute that instruction. Note that any instruction could be used (except El or DI, the instructions which enable or disable interrupts), but the RESTART and CALL instructions are the most logical choices. Also notice that the CPU inhibited the incrementing of the program counter (PC) during the three INA cycles, so that the correct PC value can be pushed onto the stack during  $M_4$  and  $M_5$ .

During  $M_4$  and  $M_5$ , the CPU performs MEMORY WRITE machine cycles to write the upper and then lower bytes of the PC onto the top of the stack. The CPU then places the two bytes accessed in  $M_2$  and  $M_3$  into the lower and upper bytes of the PC. This has the effect of jumping the execution of the program to the location specified by the CALL instruction.

FIGURE 2-18 INTERRUPT ACKNOWLEDGE MACHINE CYCLES (WITH CALL INSTRUCTION IN RESPONSE TO INTR)

#### 2.3.5 Bus Idle (BI) and HALT State

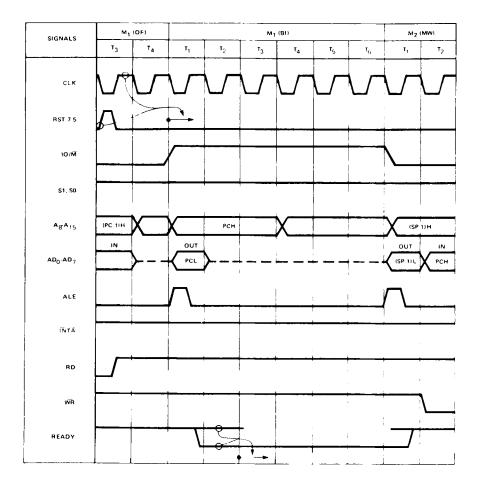

Most machine cycles of the 8085A are associated with either a READ or WRITE operation. There are two exceptions to this rule. The first exception takes place during  $M_2$  and  $M_3$  of the DAD instruction. The 8085A requires six internal T states to execute a DAD instruction, but it is not desirable to have  $M_1$  be ten (four normal plus six extra) states long. Therefore, the CPU generates two extra machine cycles that do not access either the memory or the I/O. These cycles are referred to as BUS IDLE (BI) machine cycles. In the case of DAD, they are identical to MR cycles except that RD remains high and ALE is not generated. Note that READY is ignored during  $M_2$  and  $M_3$  of DAD. The other time when the BUS IDLE machine cycle occurs is during the internal opcode generation for the RST or TRAP interrupts. Figure 2-19 illustrates the BI cycle generated in response to RST 7.5. Since this interrupt is rising-edgetriggered, it sets an internal latch; that latch is sampled at the falling edge of the next to the last T-state of the previous instruction. At this point the CPU must generate its own internal **RESTART** instruction which will (in subsequent machine cycles) cause the processor to push the program counter on the stack and to vector to location 3CH. To do this, it executes an OF machine cycle without issuing RD, generating the RESTART opcode instead. After M1, the CPU continues execution normally in all respects except that the state of the READY line is ignored during the BI cycle.

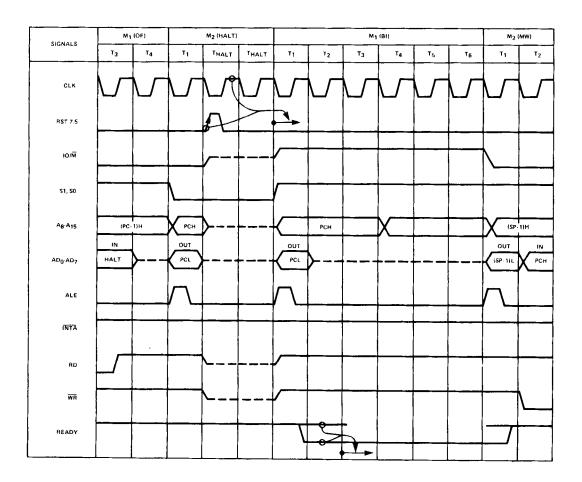

### FIGURE 2-19 RST 7.5 BUS IDLE MACHINE CYCLE

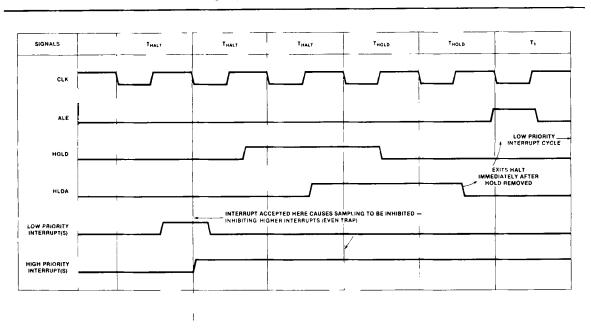

Figure 2-20 illustrates the BI cycle generated in response to RST 7.5 when a HALT instruction has just been executed and the CPU is in the  $T_{HALT}$  state, with its various signals floating. There are only two ways the processor can completely exit the  $T_{HALT}$  state, as shown in Figure 2-11. The first way is for RESET to occur, which always forces the 8085A to  $T_{RESET}$ . The second way to exit  $T_{HALT}$  permanently is for a valid interrupt to occur, which will cause the CPU to disable further interrupts by resetting INTE FF, and to then proceed to M<sub>1</sub> • T<sub>1</sub> of the next instruction. When the HOLD input is activated, the CPU will exit  $T_{HALT}$  for the duration of  $T_{HOLD}$  and then return to  $T_{HALT}$ .

In Figure 2-20 the RST 7.5 line is pulsed during  $T_{HALT}$ . Since RST 7.5 is a rising-edge-triggered interrupt, it will set an internal latch which is sampled during CLK = "1" of every  $T_{HALT}$  state (as well as during CLK = "1" two T states before any  $M_1 \cdot T_1$ .) The fact that the latched interrupt was high (assuming that INTE FF = 1 and the RST 7.5 mask = 0) will force the CPU to exit the  $T_{HALT}$  state at the end of the next CLK period, and to enter  $M_1 \cdot T_1$ .

This completes our analysis of the timing of each of the seven types of machine cycles.

### FIGURE 2-20 HALT STATE AND BUS IDLE MACHINE CYCLE RST 7.5 TERMINATES $T_{\mbox{HALT}}$ STATE

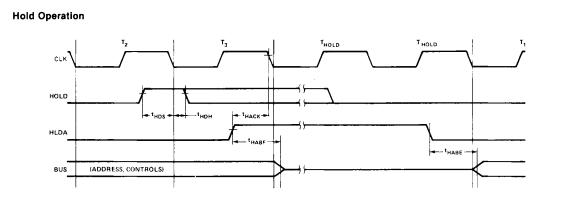

### 2.3.6 HOLD and HALT States

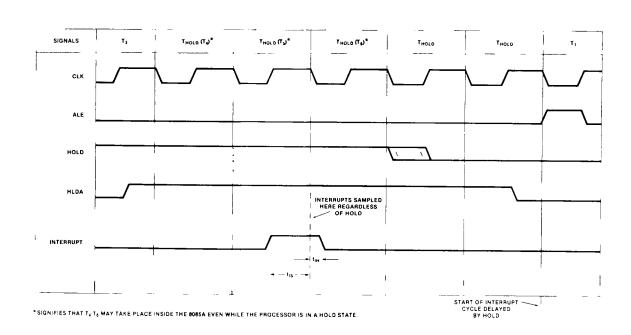

The 8085A uses the  $T_{HOLD}$  state to momentarily cease executing machine cycles, allowing external devices to gain control of the bus and peform DMA cycles. The processor internally latches the state of the HOLD line and the unmasked interrupts during CLK = "1" of every  $T_{HALT}$  state. If the internal latched HOLD signal is high during CLK = "1" of any  $T_{HALT}$  state, the CPU will exit  $T_{HALT}$  and enter  $T_{HOLD}$  on the following CLK = "1". As shown in Figure 2-21 this will occur even if a valid interrupt occurs simultaneously with the HOLD signal.

The state of the HOLD and the unmasked interrupt lines is latched internally during CLK = 1 of each  $T_{HOLD}$  state as well as during  $T_{HALT}$ states. If the internal latched HOLD signal is low during CLK = 1, the CPU will exit  $T_{HOLD}$  and enter  $T_{HALT}$  on the following CLK = 1. The 8085A accepts the first unmasked, enabled interrupt sampled; thereafter, all interrupt sampling is inhibited. The interrupt thus accepted will inevitably be executed when the CPU exits the HOLD state, even at the expense of holding off higher-priority interrupts (including TRAP). (See Figure 2-22.)

When the CPU is not in  $T_{HALT}$  or  $T_{HOLD}$ , it internally latches the HOLD line only during CLK = 1 of the last state before  $T_3$  ( $T_2$  or  $T_{WAIT}$ ) and during CLK = 1 of the last state before  $T_5$  ( $T_4$  of a six T-state M\_1). If the internal latched HOLD signal is high during the next CLK = 1, the CPU will enter  $T_{HOLD}$  after the following clock. When the CPU is not in  $T_{HALT}$  or  $T_{HOLD}$ , it will internally latch the state of the unmasked interupts only during CLK of the next to the last state before each  $M_1 \cdot T_1$ .

FIGURE 2-21 HOLD VS INTERRUPT --- NON HALT

### 2.3.7 Power On and RESET IN

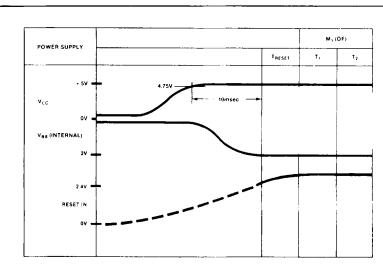

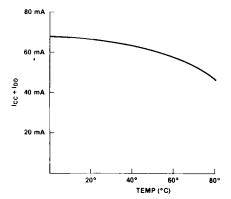

The 8085A employs a special internal circuit to increase its speed. This circuit, which is called a substrate bias generator, creates a negative voltage which is used to negatively bias the substrate. The circuit employs an oscillator and a charge pump which require a certain amount of time after POWER ON to stabilize. (See Figure 2-23.)

Taking this circuit into account, the 8085A is not guaranteed to work until 10 ms after  $V_{CC}$ reaches 4.75V. For this reason, it is suggested that RESET IN be kept low during this period. Note that the 10 ms period does not include the time it takes for the power supply to reach its 4.75V level — which may be milliseconds in some systems. A simple RC network (Figure 3-6) can satisfy this requirement.

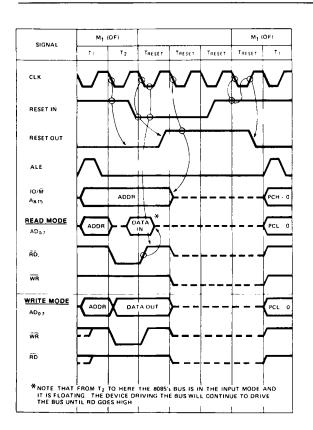

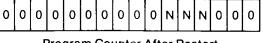

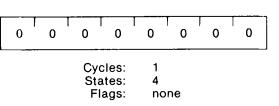

The RESET IN line is latched every CLK = 1. This latched signal is recognized by the CPU during CLK = 1 of the next T state. (See Figure 2-24.) If it is low, the CPU will issue RESET OUT and enter  $T_{HALT}$  for the next T state. RESET IN should be kept low for a minimum of three clock periods to ensure proper synchronization of the CPU. When the RESET IN signal goes high, the CPU will enter  $M_1 \cdot T_1$  for the next T state. Note that the various signals and buses are floated in  $T_{\text{RESET}}$  as well as  $T_{\text{HALT}}$  and  $T_{\text{HOLD}}$ . For this reason, it is desirable to provide pull-up resistors for the main control signals (particularly WR).

Specifically, the **RESET IN** signal causes the following actions:

| RESETS               | SETS         |

|----------------------|--------------|

| PROGRAM COUNTER      | RST 5.5 MASK |

| INSTRUCTION REGISTER | RST 6.5 MASK |

| INTE FF              | RST 7.5 MASK |

| RST 7.5 FF           |              |

| TRAP FF              |              |

| SOD FF               |              |

| MACHINE STATE FF's   |              |

| MACHINE CYCLE FF's   |              |

| INTERNALLY LATCHED   |              |

| FF's for HOLD, INTR, |              |

| and READY            |              |

**RESET IN** does not explicitly change the contents of the 8085A registers (A, B, C, D, E, H, L) and the condition flags, but due to RESET IN occurring at a random time during instruction execution, the results are indeterminate.

### FIGURE 2-23 POWER-ON TIMING

FIGURE 2-24 RESET IN TIMING

Following RESET, the 8085A will start executing instructions at location 0 with the interrupt system disabled, as shown in Figure 2-24.

Figure 2-24 also shows READ and WRITE operations being terminated by a RESET signal. Note that a RESET may prematurely terminate any READ or WRITE operation in process when the RESET occurs.

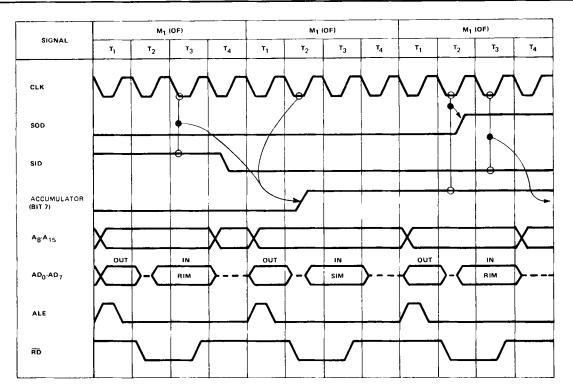

### 2.3.8 SID and SOD Signals:

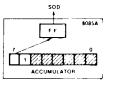

Figure 2-25 shows the timing relationship of the SID and SOD signals to the RIM and SIM instructions. The 8085A has the ability to read the SID line into the accumulator bit 7 using RIM instructions. The state of the SID line is latched internally during  $T_3 \cdot CLK = 0$  of the RIM instruction. Following this, the state of the interrupt pins and masks are also transferred directly to the accumulator.

The 8085A can set the SOD flip-flop from bit 7 of the accumulator using the SIM instruction. (See Figure 2-26.) The data is transferred from the accumulator bit 7 to SOD during  $M_1 \cdot T_2 \cdot CLK = 0$  of the instruction following SIM, assuming that accumulator bit 6 is a 1. Accumulator bit 6 is a "serial output enable" bit.

FIGURE 2-25 RELATIONSHIP OF SID AND SOD SIGNALS TO RIM AND SIM INSTRUCTIONS

FIGURE 2-26 EFFECT OF RIM AND SIM INSTRUCTIONS

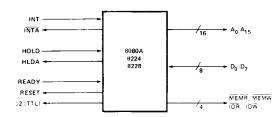

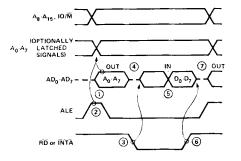

### 2.4 COMPARISON OF MCS-80 AND MCS-85 SYSTEM BUSES

This section compares the MCS-80 bus with the MCS-85 bus. Figure 2-28 details the signals and general timing of the two buses; the timing diagrams are drawn to the same scale (8080A clock cycle = 480 ns and 8085A clock cycle = 320 ns) to facilitate comparison.

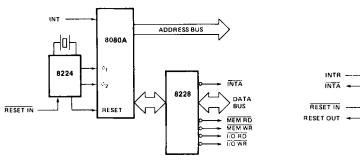

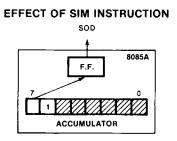

### MCS-80<sup>™</sup> System Bus

The MCS-80 bus is terminated on one end by the CPU-GROUP (consisting of the 8080A, 8224, 8228) and on the other end by the various memory and I/O circuits. The following figure shows the major signals of the MCS-80 bus.

### **FIGURE 2-27 COMPARISON OF SYSTEM BUSES**

### MCS-80<sup>™</sup> System Bus

| SIGNAL(S)                                    | FUNCTION                                                                                                                                                                            |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A <sub>0</sub> -A <sub>15</sub>              | The 16 lines of the address<br>bus identify a memory or I/O<br>location for a data transfer<br>operation.                                                                           |

| D <sub>0</sub> -D <sub>7</sub>               | The 8 lines of the data bus<br>are used for the parallel<br>transfer of data between<br>two devices.                                                                                |

| MEMR, MEMW,<br>IOR, IOW, INTA                | These five control lines<br>(MEMORY READ, MEMORY<br>WRITE, I/O READ, I/O WRITE,<br>and INTERRUPT ACKNOWL-<br>EDGE) identify the type and<br>timing of a data transfer<br>operation. |

| READY, RESET,<br>HOLD, HLDA<br>φ2 (TTL), INT | These signals are used for<br>the synchronization of slow<br>speed memories, system<br>reset, DMA, sytem timing,<br>and CPU interrupt.                                              |

|                                              |                                                                                                                                                                                     |

#### MCS-85<sup>™</sup> System Bus

The MCS-85 bus is terminated on one end by the 8085A and the other end by various memory and I/O devices. The MCS-85 bus may be optionally de-multiplexed with an 8212 eight bit latch to provide an MCS-80 type bus. The following figure shows the major signals of the MCS-85 bus.

### MCS-85<sup>™</sup> System Bus

| SIGNAL(S)                                     | FUNCTION                                                                                                                                                                                                                                                                                               |

|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A <sub>8</sub> -A <sub>15</sub>               | These are the high order<br>eight bits of the address,<br>and are used to identify a<br>memory or I/O location for a<br>data transfer cycle.                                                                                                                                                           |

| AD <sub>0</sub> -AD <sub>7</sub>              | These eight lines serve a<br>dual function. During the<br>beginning of a data transfer<br>operation, these lines carry<br>the low order eight bits of<br>the address bus. During the<br>remainder of the cycle,<br>these lines are used for the<br>parallel transfer of data be-<br>tween two devices. |

| RD, WR, INTA                                  | These signals identify the type and timing of a data transfer cycle.                                                                                                                                                                                                                                   |

| Ю/М                                           | The I/O/MEMORY line iden-<br>tifies a data transfer as be-<br>ing in the I/O address space<br>or the memory address<br>space.                                                                                                                                                                          |

| ALE                                           | ADDRESS LATCH ENABLE enables the latching of the $A_0$ - $A_7$ signals.                                                                                                                                                                                                                                |

| READY, RESET<br>OUT, HOLD,<br>HLDA, CLK, INTR | These signals are used for<br>the synchronization of slow<br>speed memories, system<br>reset, DMA, system timing<br>and CPU interrupt.                                                                                                                                                                 |

FIGURE 2-28 COMPARISON OF SYSTEM BUSES

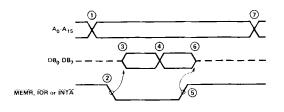

### MCS-80<sup>™</sup> System Bus for READ CYCLE

The basic timing of the MCS-80 BUS for a READ CYCLE is as follows:

The MCS-80 first presents the address () and shortly thereafter the control signal (2). The data bus, which was in the high impedance state, is driven by the selected device (3). The selected device eventually presents the valid data to the processor (4). The processor raises the control signal (5), which causes the selected device to put the data bus in the high impedance state (6). The processor then changes the address (7) for the start of the next data transfer.

### MCS-80<sup>™</sup> System Bus for WRITE CYCLE

The basic timing of the MCS-80 BUS for a WRITE CYCLE is as follows:

The MCS-80 first presents the address (1), then enables the data bus driver (2), and later presents the data (3). Shortly thereafter, the MCS-80 drops the control signal (4) for an interval of time and then raises the signal (5). The MCS-80 then changes the address (6) in preparation for the next data transfer. The advance write signal of the 8238 is also shown (7).

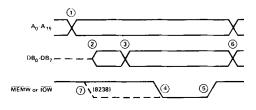

### MCS-85<sup>™</sup> System Bus for READ CYCLE

The basic timing of the MCS-85 BUS for a READ CYCLE is as follows:

At the beginning of the READ cycle, the 8085A sends out all 16 bits of address (1). This is followed by ALE (2) which causes the lower eight bits of address to be latched in either the 8155/56, 8355, 8755A, or in an external 8212. RD is then dropped (3) by the 8085A. The data bus is then tri-stated by the 8085A in preparation for the selected device driving the bus (4); the selected device will continue to drive the bus with valid data (5), until RD is raised (6) by the 8085A. At the end of the READ CYCLE (7), the address and data lines are changed in preparation for the next cycle.

### MCS-85<sup>™</sup> System Bus for WRITE CYCLE

The basic timing of the MCS-85 BUS for a WRITE CYCLE is as follows:

The timing of the WRITE CYCLE is identical to the MCS-85 READ CYCLE with the exception of the AD<sub>0</sub>-AD<sub>7</sub> lines. At the-beginning of the cycle (1), the low order eight bits of address are on AD<sub>0</sub>-AD<sub>7</sub>. After ALE drops, the eight bits of data (2) are put on AD<sub>0</sub>-AD<sub>7</sub>. They are removed (3) at the end of the WRITE CYCLE, in anticipation of the next data transfer.

FIGURE 2-28 (Continued) COMPARISON OF SYSTEM BUSES

The following observations of the two buses can be made:

- 1. The access times from address leaving the processor to returning data are almost identical, even though the 8085A is operating 50% faster than the 8080.

- 2. With the addition of an 8212 latch to the 8085A, the basic timings of the two systems are very similar.

- 3. The 8085A has more time for address setup to RD than the 8080.

- 4. The MCS-80 has a wider  $\overline{\text{RD}}$  signal, but a narrower  $\overline{\text{WR}}$  signal than the 8085A.

- 5. The MCS-80 provides stable data setup to the leading and trailing edges of WR, while the 8085 provides stable data setup to only the trailing edge of WR.

- 6. The MCS-80 control signals have different widths and occur at different points in the machine cycle, while the 8085A control signals have identical timing.

- While not shown on the chart, the MCS-80 data and address hold times are adversely affected by the processor preparing to enter the HOLD state. The 8085A has identical timing regardless of entering HOLD.

- 8. Also not shown on the chart is the fact that all output signals of the 8085A have  $-400\mu a$  of source current and 2.0 ma of sink current. The 8085A also has input voltage levels of V<sub>IL</sub> = 0.8V and V<sub>IH</sub> = 2.0V.

### CONCLUSION:

The preceding discussion has clearly shown that the MCS-85 bus satisfies the two restrictions of COMPATIBILITY and SPEED. It is compatible because it requires only an 8212 latch to generate an MCS-80 type bus. If the four control signals MEMR, MEMW, IOR and IOW are desired, they can be generated from RD, WR, and  $IO/\overline{M}$  with a decoder or a few gates. The MCS-85 bus is also fast. While running at 3MHz, the 8085A generates better timing signals than the MCS-80 does at 2MHz. Furthermore, the multiplexed bus structure doesn't slow the 8085A down, because it is using the internal states to overlap the fetch and execution portions of different machine cycles. Finally, the MCS-85 can be slowed down or sped up considerably, while still providing reasonable timing.

TO USE. The RD, WR, and INTA control signals all have identical timing, which isn't affected by the CPU preparing to enter the HOLD state. Furthermore, the address and data bus have good setup and hold times relative to the control signals. The voltage and current levels for the interface signals will all drive buses of up to 40 MOS devices, or 1 schottky TTL device.

The MCS-85 system bus is also EFFICIENT. Efficiency is the reason that the lower eight address lines are multiplexed with the data bus. Every chip that needs to use both A<sub>0</sub>-A<sub>7</sub> and D<sub>0</sub>-D<sub>7</sub> saves 7 pins (the eighth pin is used for ALE) on the interface to the processor. That means that 7 more pins per part are available to either add features to the part or to use a smaller package in some cases. In the three chip system shown in Figure 3-6, the use of the MCS-85 bus saves  $3 \times 7 = 21$  pins, which are used for extra I/O and interrupt lines. A further advantage of the MCS-85 bus is apparent in Figure 3-7, which shows a printed circuit layout of the circuit in Figure 3-6. The reduced number of pins and the fact that compatible pinouts were used, provides for an extremely compact, simple, and efficient printed circuit. Notice that great care was taken when the pinouts were assigned to ensure that the signals would flow easily from chip to chip to chip.

### APPENDIX C

### 8085 Instruction Set

The following pages are reprinted with the permission of Intel Corporation.

### 8085A INSTRUCTION SET

### 5.1 WHAT THE INSTRUCTION SET IS

A computer, no matter how sophisticated, can do only what it is instructed to do. A program is a sequence of instructions, each of which is recognized by the computer and causes it to perform an operation. Once a program is placed in memory space that is accessible to your CPU, you may run that same sequence of instructions as often as you wish to solve the same problem or to do the same function. The set of instructions to which the 8085A CPU will respond is permanently fixed in the design of the chip.

Each computer instruction allows you to initiate the performance of a specific operation. The 8085A implements a group of instructions that move data between registers, between a register and memory, and between a register and an I/O port. It also has arithmetic and logic instructions, conditional and unconditional branch instructions, and machine control instructions. The CPU recognizes these instructions only when they are coded in binary form.

### 5.2 SYMBOLS AND ABBREVIATIONS:

The following symbols and abbreviations are used in the subsequent description of the 8085A instructions:

| SYMBOLS     | MEANING                                 | RP |

|-------------|-----------------------------------------|----|

| accumulator | Register A                              |    |

| addr        | 16-bit address quantity                 |    |

| data        | 8-bit quantity                          |    |

| data 16     | 16-bit data quantity                    |    |

| byte 2      | The second byte of the instruc-<br>tion |    |

| byte 3      | The third byte of the instruc-<br>tion  | rh |

| port        | 8-bit address of an I/O device          | rl |

| r,r1,r2     | One of the registers A,B,C,<br>D,E,H,L  |    |

DDD,SSS

rp

RP

The bit pattern designating one of the registers A,B,C,D, E,H,L (DDD = destination, SSS = source):

| DDD or<br>SSS | REGISTER<br>NAME |

|---------------|------------------|

| 111           | А                |

| 000           | В                |

| 001           | С                |

| 010           | D                |

| 011           | E                |

| 100           | н                |

| 101           | L                |

One of the register pairs:

B represents the B,C pair with B as the high-order register and C as the low-order register;

D represents the D,E pair with D as the high-order register and E as the low-order register;

H represents the H,L pair with H as the high-order register and L as the low-order register;

SP represents the 16-bit stack pointer register.

The bit pattern designating one of the register pairs B,D,H,SP:

| RP | REGISTER<br>PAIR |

|----|------------------|

| 00 | B-C              |

| 01 | D-E              |

| 10 | H-L              |

| 11 | SP               |

The first (high-order) register of a designated register pair. The second (low-order) register of a designated register pair.

| PC       | 16-bit program counter<br>register (PCH and PCL are<br>used to refer to the high-order<br>and low-order 8 bits respec-<br>tively). |

|----------|------------------------------------------------------------------------------------------------------------------------------------|

| SP       | 16-bit stack pointer register<br>(SPH and SPL are used to refer<br>to the high-order and low-order<br>8 bits respectively).        |

| rm       | Bit m of the register r (bits are<br>number 7 through 0 from left<br>to right).                                                    |

| LABEL    | 16-bit address of subroutine.                                                                                                      |

|          | The condition flags:                                                                                                               |

| Z        | Zero                                                                                                                               |

| S        | Sign                                                                                                                               |

| Р        | Parity                                                                                                                             |

| CY       | Carry                                                                                                                              |

| AC       | Auxiliary Carry                                                                                                                    |

| ()       | The contents of the memory location or registers enclosed in the parentheses.                                                      |

| ⊷        | "Is transferred to"                                                                                                                |

| Λ        | Logical AND                                                                                                                        |

| ∀        | Exclusive OR                                                                                                                       |

| $\wedge$ | Inclusive OR                                                                                                                       |

| +        | Addition                                                                                                                           |

| -<br>•   | Two's complement subtraction                                                                                                       |

| *        | Multiplication                                                                                                                     |

| ↔        | "Is exchanged with"                                                                                                                |

|          | The one's complement (e.g., $\overline{(A)}$ )                                                                                     |

| n        | The restart number 0 through 7                                                                                                     |

| NNN      | The binary representation 000<br>through 111 for restart number<br>0 through 7 respectively.                                       |

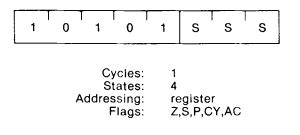

The instruction set encyclopedia is a detailed description of the 8085A instruction set. Each instruction is described in the following manner:

- 1. The MCS-85 macro assembler format, consisting of the instruction mnemonic and operand fields, is printed in **BOLDFACE** on the first line.

- 2. The name of the instruction is enclosed in parentheses following the mnemonic.

- 3. The next lines contain a symbolic description of what the instruction does.

- 4. This is followed by a narrative description of the operation of the instruction.

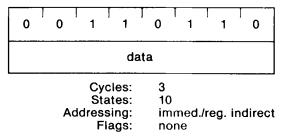

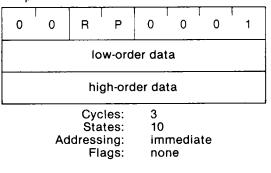

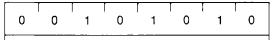

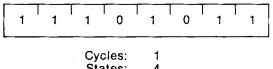

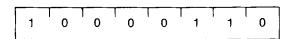

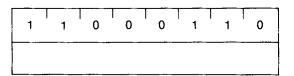

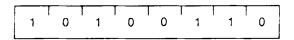

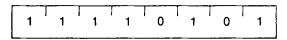

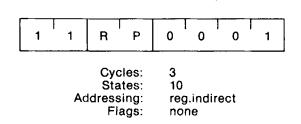

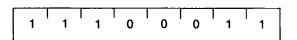

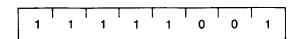

- 5. The boxes describe the binary codes that comprise the machine instruction.

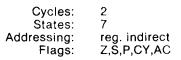

- 6. The last four lines contain information about the execution of the instruction. The number of machine cycles and states required to execute the instruction are listed first. If the instruction has two possible execution times, as in a conditional jump, both times are listed, separated by a slash. Next, data addressing modes are listed if applicable. The last line lists any of the five flags that are affected by the execution of the instruction.

#### 5.3 INSTRUCTION AND DATA FORMATS

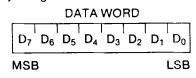

Memory used in the MCS-85 system is organized in 8-bit bytes. Each byte has a unique location in physical memory. That location is described by one of a sequence of 16-bit binary addresses. The 8085A can address up to 64K (K = 1024, or  $2^{10}$ ; hence, 64K represents the decimal number 65,536) bytes of memory, which may consist of both random-access, read-write memory (RAM) and read-only memory (ROM), which is also random-access.

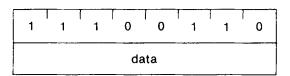

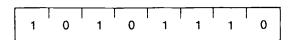

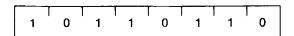

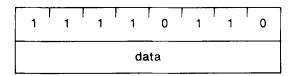

Data in the 8085A is stored in the form of 8-bit binary integers:

When a register or data word contains a binary number, it is necessary to establish the order in which the bits of the number are written. In the Intel 8085A, BIT 0 is referred to as the **Least Significant Bit (LSB)**, and BIT 7 (of an 8-bit number) is referred to as the **Most Significant Bit (MSB)**.

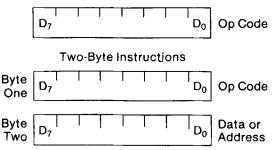

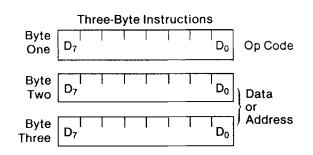

An 8085A program instruction may be one, two or three bytes in length. Multiple-byte instructions must be stored in successive memory locations; the address of the first byte is always used as the address of the instruction. The exact instruction format will depend on the particular operation to be executed.

Single Byte Instructions

## THE INSTRUCTION SET

#### 5.4 ADDRESSING MODES:

Often the data that is to be operated on is stored in memory. When multi-byte numeric data is used, the data, like instructions, is stored in successive memory locations, with the least significant byte first, followed by increasingly significant bytes. The 8085A has four different modes for addressing data stored in memory or in registers:

- Direct Bytes 2 and 3 of the instruction contain the exact memory address of the data item (the loworder bits of the address are in byte 2, the high-order bits in byte 3).

- Register The instruction specifies the register or register pair in which the data is located.

- Register Indirect The instruction specifies a register pair which contains the memory address where the data is located (the high-order bits of the address are in the first register of the pair the low-order bits in the second).

- Immediate The instruction contains the data itself. This is either an 8-bit quantity or a 16-bit quantity (least significant byte first, most significant byte second).

Unless directed by an interrupt or branch institution, the execution of instructions proceeds through consecutively increasing memory locations. A branch instruction can specify the address of the next instruction to be executed in one of two ways:

Direct — The branch instruction contains the address of the next instruction to be executed. (Except for the 'RST' instruction, byte 2 contains the low-order address and byte 3 the high-order address.)  Register Indirect — The branch instruction indicates a register-pair which contains the address of the next instruction to be executed. (The high-order bits of the address are in the first register of the pair, the loworder bits in the second.)

The RST instruction is a special one-byte call instruction (usually used during interrupt sequences). RST includes a three-bit field; program control is transferred to the instruction whose address is eight times the contents of this three-bit field.

#### 5.5 CONDITION FLAGS:

There are five condition flags associated with the execution of instructions on the 8085A. They are Zero, Sign, Parity, Carry, and Auxiliary Carry. Each is represented by a 1-bit register (or flip-flop) in the CPU. A flag is set by forcing the bit to 1; it is reset by forcing the bit to 0.

Unless indicated otherwise, when an instruction affects a flag, it affects it in the following manner:

- Zero: If the result of an instruction has the value 0, this flag is set; otherwise it is reset.

- Sign: If the most significant bit of the result of the operation has the value 1, this flag is set; otherwise it is reset.

- Parity: If the modulo 2 sum of the bits of the result of the operation is 0, (i.e., if the result has even parity), this flag is set; otherwise it is reset (i.e., if the result has odd parity).

- Carry: If the instruction resulted in a carry (from addition), or a borrow (from subtraction or a comparison) out of the high-order bit, this flag is set; otherwise it is reset.

- Auxiliary Carry: If the instruction caused a carry out of bit 3 and into bit 4 of the resulting value, the auxiliary carry is set; otherwise it is reset. This flag is affected by single-precision additions, subtractions, increments, decrements, comparisons, and logical operations, but is principally used with additions and increments preceding a DAA (Decimal Adjust Accumulator) instruction.

#### 5.6 INSTRUCTION SET ENCYCLOPEDIA

In the ensuing dozen pages, the complete 8085A instruction set is described, grouped in order under five different functional headings, as follows:

- 1. Data Transfer Group Moves data between registers or between memory locations and registers. Includes moves, loads, stores, and exchanges. (See below.)

- 2. Arithmetic Group Adds, subtracts, increments, or decrements data in registers or memory. (See page 5-13.)

- 3. Logic Group ANDs, ORs, XORs, compares, rotates, or complements data in registers or between memory and a register. (See page 5-16.)

- 4. **Branch Group** Initiates conditional or unconditional jumps, calls, returns, and restarts. (See page 5-20.)

- 5. Stack, I/O, and Machine Control Group — Includes instructions for maintaining the stack, reading from input ports, writing to output ports, setting and reading interrupt masks, and setting and clearing flags. (See page 5-22.)

The formats described in the encyclopedia reflect the assembly language processed by Intel-supplied assembler, used with the Intellec<sup>®</sup> development systems.

#### 5.6.1 Data Transfer Group

This group of instructions transfers data to and from registers and memory. **Condition flags are not affected by any instruction in this group.**

| MOV r1, r2 | (Move Register) |

|------------|-----------------|

| (+1) (+0)  | (more neglecci) |

$(r1) \leftarrow (r2)$

The content of register r2 is moved to register r1.

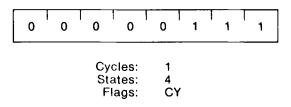

| 0 | 1                                           | D | D            | D                      | S      | S      | S   |

|---|---------------------------------------------|---|--------------|------------------------|--------|--------|-----|

|   | Cycles:<br>States:<br>Addressing:<br>Flags: |   | tes:<br>ing: | 1<br>4 ((<br>reç<br>no | gister | 5 (808 | 30) |

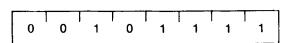

MOV r, M (Move from memory) (r) ← ((H) (L)) The content of the memory location, whose address is in registers H and L, is moved to register r.

| 0           | r                  | D | D   | D       | 1    | 1 | 0 |

|-------------|--------------------|---|-----|---------|------|---|---|

|             | Cycles:<br>States: |   |     |         |      |   |   |

|             |                    |   |     | 7       |      |   |   |

| Addressing: |                    |   | reg | g. indi | rect |   |   |

| Flags:      |                    |   |     | no      | ne   |   |   |

MOV M, r (Move to memory) ((H)) (L)) ← (r)

The content of register r is moved to the memory location whose address is in registers H and L.

| 0 | 1 | 1   | 1    | 0 | S | s | S |

|---|---|-----|------|---|---|---|---|

| , |   | Сус | les. | 2 |   |   |   |

| Cycles.     | 2             |

|-------------|---------------|

| States:     | 7             |

| Addressing: | reg. indirect |

| Flags:      | none          |

MVI r, data (Move Immediate)

(r) - (byte 2)

The content of byte 2 of the instruction is moved to register r.

| 0    | 0 | D | D | D | 1 | 1 | 0 |

|------|---|---|---|---|---|---|---|

| data |   |   |   |   |   |   |   |

| Cycles:     | 2         |

|-------------|-----------|

| States:     | 7         |

| Addressing: | immediate |

| Flags:      | none      |

MVI M, data (Move to memory immediate) ((H) (L)) - (byte 2)

The content of byte 2 of the instruction is moved to the memory location whose address is in registers H and L.

### THE INSTRUCTION SET

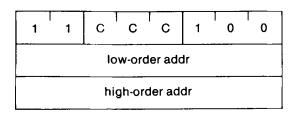

LXI rp, data 16 (Load register pair immediate) (rh) ← (byte 3), (rl) ← (byte 2)

(rl)  $\leftarrow$  (byte 2) Byte 3 of the instruction is moved into the high-order register (rh) of the register pair rp. Byte 2 of the instruction is moved into the low-order register (rl) of the register pair

rp.

LDA addr (Load Accumulator direct) (A) ← ((byte 3)(byte 2)) The content of the memory location, whose address is specified in byte 2 and byte 3 of

the instruction, is moved to register A.

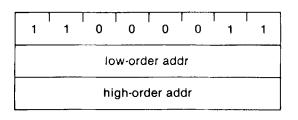

| 0               | 0 | 1 | 1 | 1 | 0 | 1 | 0 |

|-----------------|---|---|---|---|---|---|---|

| low-order addr  |   |   |   |   |   |   |   |

| high-order addr |   |   |   |   |   |   |   |

Cycles: 4 States: 13 Addressing: direct Flags: none

STA addr (Store Accumulator direct) ((byte 3)(byte 2)) ← (A) The content of the accumulator is moved to

the memory location whose address is specified in byte 2 and byte 3 of the instruction.

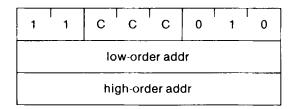

| 0               | 0 | 1 | 1 | 0 | 0 | 1 | 0 |

|-----------------|---|---|---|---|---|---|---|

| low-order addr  |   |   |   |   |   |   |   |

| high-order addr |   |   |   |   |   |   |   |

| Cycles: 4       |   |   |   |   |   |   |   |

| Cycles:     | 4      |

|-------------|--------|

| States:     | 13     |

| Addressing: | direct |

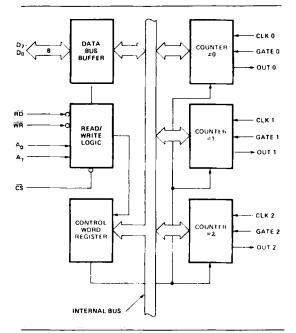

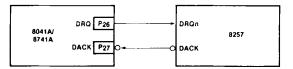

| Flags:      | none   |