# 12 MHz Zero-Wait 80286 Turbo Main Board

**MBVLSI-168 (V.2)**

The information in this manual is subject to change without notice.

#### TABLE OF CONTENTS

| I.    | GENERAL SPECIFICATION                              |   |

|-------|----------------------------------------------------|---|

| 11.   | MAIN BOARD JUMPER SELECT 4–7                       | ( |

| Ш.    | MEMORY COMBINATION 8-9                             |   |

| IV.   | HOW TO CHANGE THE SYSTEM SPEED<br>BY SOFTWARE      |   |

| V.    | SYSTEM MEMORY MAP11                                |   |

| VI.   | I/O CHANNEL SLOTS                                  |   |

| VII.  | HARDWARE COMPATIBILITY                             |   |

| VIII. | ATTACHMENT I:<br>FUNCTION OF JP13/JP14/JP15/JP1822 | ( |

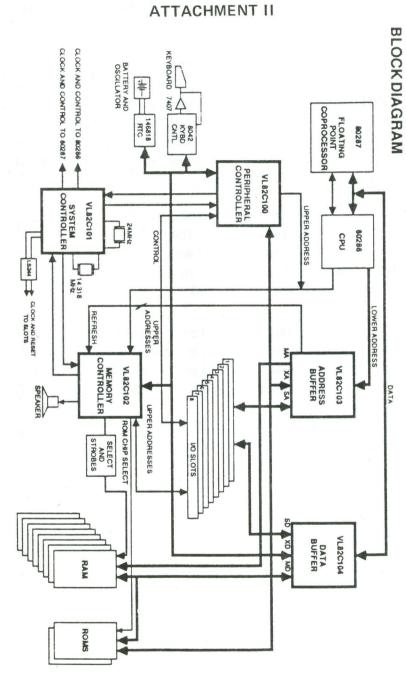

|       | ATTACHMENT II:<br>BLOCKDIAGRAM                     |   |

|       | ATTAQUATENT UL                                     |   |

ATTACHMENT III: BOARD LAYOUT AND JUMPER POSITION . . 24

#### WHAT WE POSSESSIVE THAT OTHERS WITHOUT !

- \* 5 chips set full CMOS process low power consumption

- \* Zero wait state read operations

- \* One wait state write operations

- \* 20 mA, 200pF slot drive (system bus) capability

- \* 8 mA, 150pF DRAM drive capability

- \* Four layer implementation for low noise operation.

- Most powerful memory combination available: —Using 44256/41256 memory chip, up to 512K/1024K —Using 4164/41256/1M bit memory chip, up to

- 512K/640K/1024K/2048K/4096K

- -Using RAM Modular, UP TO 512K/1024K/2048K/ 4096K

| * * * * * * * * * * * * * * * * * * * * | * * * |

|-----------------------------------------|-------|

| *                                       | *     |

| * NOTE: In this manual,                 | *     |

| * 80286: means Personal Computers that  | *     |

| * use 80286 CPU                         | *     |

| *                                       | *     |

# I. GENERAL SPECIFICATION

- \* Fully compatible with 80286 system

- \* 8/12 MHz speed hardware and software selectable

- \* RAM access time 0-wait and 1-wait switchable

- \* Up to 4 mega byte memory on board

- \* 16 mega byte expandable memory in the protect, virtual address mode

- \* 2 sockets for BIOS.

- \* 8 I/O expansion slots

- \* Socket for 80287 math processor

- \* CMOS clock and calendar circuit with rechargable battery support

- \* 24-bit addressing and 16-bit data path capabilities

- \* 16-level interrupts

- \* 7-channel DMA (Direct memory access)

- \* 3-programmable timers

- \* 1/0 speed: 8MHz

- \* Most powerful memory combination available: -Using 44256/41256 memory chip, up to 512K/1024K

- -Using 4164/41256/1M bit memory chip, up to 512K/640K/1024K/2048K/4096K

- -Using RAM Modular, UP TO 512K/1024K/2048K/ 4096K

#### **II. MAIN BOARD JUMPER SELECTION**

CONNECTORS AND JUMPERS:

| Power supply connector<br>Keyboard connector<br>Hardware reset switch<br>Keylock/Power LED<br>Speaker connector<br>Turbo hardware switch<br>Turbo LED indicator |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hardware reset switch<br>Keylock/Power LED<br>Speaker connector<br>Turbo hardware switch<br>Turbo LED indicator                                                 |

| Keylock/Power LED<br>Speaker connector<br>Turbo hardware switch<br>Turbo LED indicator                                                                          |

| Speaker connector<br>Turbo hardware switch<br>Turbo LED indicator                                                                                               |

| Turbo hardware switch<br>Turbo LED indicator                                                                                                                    |

| Turbo LED indicator                                                                                                                                             |

|                                                                                                                                                                 |

|                                                                                                                                                                 |

| Memory speed Jumper                                                                                                                                             |

| Memory size select                                                                                                                                              |

| Zero wait/One wait select                                                                                                                                       |

| EPROM size select                                                                                                                                               |

| Display adapter select                                                                                                                                          |

| Keyboard controller select                                                                                                                                      |

| Power good select                                                                                                                                               |

| External battery connector                                                                                                                                      |

|                                                                                                                                                                 |

\*: Jumper JP13/JP14/JP15/JP18 is default-set for software speed change, which according to the "BIOS" used in this board.

It is not necessary for user to adjust the jumper setting, unless user would like to change the "BIOS".

More technical information, please refer to ''ATTACH-MENT I''

- JP1: Hardware reset switch It's a reset button

- JP4: Turbo hardware switch It's a Turbo button

- JP5: Trubo LED indicator LED lights on for Turbo mode

- JP6: Memory speed select Short Pin 1 & Pin 2 of Jumper JP6: using 100ns speed memory chips (DEFAULT)

JP7/JP8/JP9: Memory size select

| JP7/JP8/JP9       | Amount      | (Base memory/Expansion |         |

|-------------------|-------------|------------------------|---------|

|                   | memory      |                        | memory) |

| open/short/short  | 4096K (4MB) | 640K                   | /3456K) |

| short/open/open   | 2048K (2MB) | (640K                  | /1408K) |

| short/open/short  | 1024K (1MB) | (640K                  | /384K)) |

| short/short/open  | 640K        | (640K                  | /0 )    |

| short/short/short | 512K        | (512K                  | /0 )    |

- JP10: Zero wait/One wait select Short JP10: Zero wait Open JP10: One wait

- JP11: EPROM size select Short JP11: Using 256K EPROM Open JP11: Using 128K EPROM

- JP12: Display adapter select Short JP12: Using Color display adapter Open JP12: Using Monographics display adapter

- JP16: Power good select Short Pin 1 & Pin 2 of JP16: Power good provided by Mother Board (default) Short Pin 2 & Pin 3 of JP16: Power good provided by Power supplier itself

- JP17: External battery connector The connector is for connecting for size "AA" batteries instead of the blue barrel shaped rechargable battery. Pin assignments as followings:

- PINASSIGNMENT16Vdc2Not used3GND4GND

### JP13/JP14/JP15/JP18: Keyboard controller

Jumper JP13/JP14/JP15/JP18 is default-set to

change speed via software, and which according to the ''BIOS'' used in this board.

Unless you would like to change the "BIOS", it is not necesory for you to adjust the Jumper setting. More technical information, please refer to "ATTACHMENT I".

#### **III MEMORY COMBINATION**

0

#### III-1: Using 44256/41256 memory chip combination:

| Memory size    | Jumper setting    | Bank 0<br>socket position                                  | Bank 1<br>socket position                                  |  |

|----------------|-------------------|------------------------------------------------------------|------------------------------------------------------------|--|

| 512K           | short/short/short | 44256 x 4 pcs<br>(U47-U50)<br>41256 x 2 pcs<br>(U29 & U38) |                                                            |  |

| 1024K<br>(1MB) | short/open/short  | 44256 x 4 pcs<br>(U47-U50)<br>44256 x 4 pcs<br>(U29 & U38) | 44256 x 4 pcs<br>(U41-U44)<br>41256 x 2 pcs<br>(U11 & U20) |  |

#### III-2: Using 4164/41256/1Mbbyte memory chip combination:

| Memory size    | JP7/JP8/JP9       | Bank 0                        | Bank 1                       |  |

|----------------|-------------------|-------------------------------|------------------------------|--|

| 512K           | short/short/short | 41256 x 18 pcs<br>(U21-U38)   |                              |  |

| 640K           | short/short/open  | 41256x18 pcs<br>(U21-U38)     | 4164 x 18 pcs<br>(U3-U20)    |  |

| 1024K<br>(1MB) | short/open/short  | 41256 x 18 pcs<br>(U21-U38)   | 41256 x 18 pcs<br>(U3-U20)   |  |

| 2048K<br>(2MB) | short/open/open   | 1M byte x 18 pcs<br>(U21-U38) |                              |  |

| 4096K<br>(4MB) | open/short/short  | 1M byte x 18 pcs<br>(U21-U38) | 1M byte x 18 pcs<br>(U3-U20) |  |

#### III-3 Using RAM MODULAR Chip combination:

| Memory size    | JP7/JP8/JP9       | Bank 0                     | Bank 1                       |  |

|----------------|-------------------|----------------------------|------------------------------|--|

| 512K           | short/short/short | 256K x 2 sets<br>(U1 & U2) |                              |  |

| 1024K<br>(1MB) | short/open/short  | 256Kx2 sets<br>(U1 & U2)   | 256K x 2 sets<br>(U39 & U40) |  |

| 2048K<br>(2MB) | short/open/open   | 1MB x 2 sets<br>(U1 & U2)  |                              |  |

| 4096K<br>(4MB) | open/short/short  | 1MB x 2 sets<br>(U1 & U2)  | 1MB x 2 sets<br>(39 x& U40)  |  |

| * * |               | ***************************************              |

|-----|---------------|------------------------------------------------------|

| *   |               |                                                      |

| *   | NOTE:         | User cannot combinate each of Item III-1/III-2/III-3 |

| *   |               | for total amount memory.                             |

| *   |               | Each item III-1/III-2/III-3 works independently.     |

| *   |               |                                                      |

| * * | * * * * * * * | ***************************************              |

# IV HOW TO CHANGE THE SYSTEM SPEED BY SOFTWARE

This mother board has two system clock i.e. 8MHz and 12MHz, User can change speed via hardware or software controller.

IV-1 Hardware controller:

Hardware controller: refer to JP4, press "Turbo switch button" for Turbo/Normal mode

- IV-2 Software controller:

- IV-2-1 When the equipment of mother board used "AMI BIOS" Press and hold down (CTRL) & (ALT) key and hit the (+)or (-)key for Turbo/Normal speed change.

- IV-2-2 When the equipment of mother board used "AWARD BIOS" Press and hold down (CTRL) & (ALT) key and hit the  $\langle + \rangle$  or  $\langle - \rangle$  key for Turbo/ Normal mode.

- IV-2-3 When the equipment of mother board used "PHONIX BIOS" Press and hold down (CTRL) & (ALT) key and hit the (\) key for Turbo/Normal mode.

Due to different version of PHONIX BIOS, user may press and hold down  $\langle \text{CTRL} \rangle$  &  $\langle \text{ALT} \rangle$  key and hit the  $\langle + \rangle$  or  $\langle - \rangle$  key for Turbo/Normal mode.

9

# V. SYSTEM MEMORY MA)

| ADDRESS RANGE  | START-END     | NAME    | FUNCTION               |

|----------------|---------------|---------|------------------------|

| 000000-03FFFF  | 000K-256K     | Bank 0  | System memory (256K)   |

| 040000-07FFFF  | 256K-512K     | Bank1   | System memory (256K)   |

| 080000-09FFFFF | 512K-640K     | Bank2   | System memory (128K)   |

|                |               |         |                        |

| OAFFFF-OBFFFF  | 640K-768K     | Video   | Display card buffer    |

|                | · · · ·       |         | (128K)                 |

| 0C0000-0DFFFF  | 768K-869K     | I/O ROM | Expansion ROM (128K)   |

| 0E0000-0EFFFF  | 896K - 960K   | ROM     | System usage (64K)     |

| 0F0000-0FFFFF  | 960K-1024K    | ROM     | BIOS (64K)             |

|                | i. mita       |         |                        |

| 100000-11FFFF  | 1024K-1152K   | Bank 2  | System memory (128K)   |

| 120000-15FFFF  | 1152K-1408K   | Bank 3  | System memory (128K)   |

|                |               |         |                        |

| 160000-FDFFFF  | 1408K-16146K  | RAM     | Expansion RAM (14870K) |

|                |               |         |                        |

| FE0000-FEFFFF  | 16146K-16210K | ROM     | System usage (64K)     |

| FF0000-FFFFFF  | 16210K-16274K | ROM     | BIOS (64K)             |

#### VI. I/O CHANNEL SLOTS

The I/O channel supports:

- \* I/O address space hex 100 to hex 3FF

- \* 24-bit memory addresses (16MB)

- \* Refresh of system memory from channel microprocessors

- \* Selection of data accesses (eigher 8 bit or 16 bit)

- \* Interrupt

- \* DMA channels

- \* I/O wait-state generation

- \* Open-bus structure (allowing multiple microprocessors to share the system's resources, including memory)

# I/O ADDRESS MAP

| HEX RANGE | DEVICES                     | USAGE  |

|-----------|-----------------------------|--------|

| 000-01F   | DMA controller 1            | System |

| 020-03F   | Interrupt controller 1      | System |

| 040-05F   | Timer                       | System |

| 060-06F   | 8042 (Keyboard)             | System |

| 070-07F   | Real time clock, NMI mask   | System |

| 080-09F   | DMA page register           | System |

| 0A0-0BF   | Interrupt controller 2      | System |

| 0C0-0DF   | DMA controller 2            | System |

| OFO       | Clear Math Coprocessor busy | System |

| 0F1       | Reset Math Coprocessor      | System |

| 0F8-0FF   | Math Coprocessor            | System |

| 1F0-1F8   | Fixed disk                  | 1/0    |

| 200-207   | Game I/O                    | 1/0    |

| 278-27F   | Parallel printer port 2     | 1/0    |

| 2F8-2FF   | Serial port 2               | 1/0    |

| 300-31 F  | prototype card              | 1/0    |

| 360-36F   | Reserved                    | 1/0    |

#### I/O ADDRESS MAP

| HEX RANGE | DEVICES                                | USAGE |

|-----------|----------------------------------------|-------|

| 378-37F   | Parallel printer port 1                | 1/0   |

| 380-38F   | SDLC, bisynchronus 2                   | 1/0   |

| 3A0-3AF   | Bisynchronus 1                         | 1/0   |

| 3B0-3BF   | Monochrome display and printer adapter | 1/0   |

| 3C0-3CF   | Reserved                               | 1/0   |

| 3D0-3DF   | Color/graphic monitor adapter          | 1/0   |

| 3F0-3F7   | Floppy diskette controller             | 1/0   |

| 3F8-3FF   | Serial port 1                          | 1/0   |

# Numbering of the I/O slots is as follows:

REARPANEL

| GND       | B1  | T  | E   | A1  | -1/0 CH CK  |

|-----------|-----|----|-----|-----|-------------|

| RESET DRV | B2  | 1  | 1   | A2  | SD7         |

| +5Vdc     | B3  | 1  | I   | A3  | SD6         |

| IRQ2      | B4  | 1  | - E | A4  | SD5         |

| -5Vdc     | B5  | 1  | 1   | A5  | SD4         |

| DRQ2      | B6  | T  | 1   | A6  | SD3         |

| -12Vdc    | B7  | L. | 1   | A7  | SD2         |

| OWS       | B8  | 1  | 1   | A8  | SD1         |

| +12Vdc    | B9  | 1  | 1   | A9  | SD0         |

| GND       | B10 | Τ. | 1   | A10 | -I/O CH RDY |

| -SMEMW    | B11 | 1  | 1   | A11 | AEN         |

| -SMEMR    | B12 | 1  | 1   | A12 | SA19        |

| -IOW      | B13 | 1  | 1   | A13 | SA18        |

| -IOR      | B14 | 1  | 1   | A14 | SA17        |

| -DCK3     | B15 | 1  | 1   | A15 | SA16        |

| DRQ3      | B16 | 1  | 1   | A16 | SA15        |

| -DACK1    | B17 | 1  | 1   | A17 | SA14        |

| DRQ1      | B18 | 1  | 1   | A18 | SA13        |

| -REFRESH  | B19 | I  | 1   | A19 | SA:12       |

| CLK       | B20 | 1  | 1   | A20 | SA11        |

| IRQ7      | B21 | 1  | 1   | A21 | SA10        |

| IRQ6      | B22 | 1  | 1   | A22 | SA9         |

| IRQ5      | B23 | 1  | 1   | A23 | SA8         |

| IRQ4      | B24 | I  | 1   | A24 | SA7         |

| IRQ3      | B25 | I  | 1   | A25 | SA6         |

| -DACK2    | B26 | 1  | 1   | A26 | SA5         |

| T/C       | B27 | I  | - I | A27 | SA4         |

| BALE      | B28 | 1  | 1   | A28 | SA3         |

| +5Vdc     | B29 | 1  | 1   | A29 | SA2         |

| OSC       | B30 | I  | 1   | A30 | SA1         |

| GND       | B31 | I  | 1   | A31 | SA0         |

|           |     |    |     |     |             |

I/O CHANNEL J1 – J8

# VII. HARDWARE COMPATIBILITY

# SYSTEM TIMERS

The system has three programmable timer/counters controlled by an Intel 8254-2 timer/counter chip. These are channels 0 through 2, defined as follows:

| Channel 0                       | System Timer                          |

|---------------------------------|---------------------------------------|

| GATE 0<br>CLK IN 0<br>CLK OUT 0 | Tied on<br>1.190 MHz OSC<br>8259A IRQ |

|                                 |                                       |

| Channel 1                       | Refresh Request Generator             |

| GATE 1                          | Tied on                               |

| GATE 1    | Tied on               |

|-----------|-----------------------|

| CLK IN 1  | 1.190MHz OSC          |

| CLK OUT 1 | Request Refresh Cycle |

Note: Channel 1 is programmed to generate a 15 microsecond period signal.

| Channel 2             | Tone Generation for Speaker                |

|-----------------------|--------------------------------------------|

| GATE 2                | Controlled by bit 0 of port hex 61 PPI bit |

| CLK IN 2<br>CLK OUT 2 | 1.190 MHz OSC<br>Used to drive the speaker |

REARPANEL

|           | 1   |     |   |     |       |

|-----------|-----|-----|---|-----|-------|

| -MEM CS16 | D1  | 1   | 1 | C1  | SBHE  |

| 1/0 CS16  | D2  | 1   | 1 | C2  | LA23  |

| IRQ16     | D3  | 1   | 1 | C3  | LA22  |

| IRQ11     | D4  | 1   | 1 | C4  | LA21  |

| IRQ12     | D5  | 1 : | 1 | C5  | LA20  |

| IRQ15     | D6  | 1   | 1 | C6  | LA19  |

| IRQ14     | D7  | 1   | 1 | C7  | LA18  |

| -DACK0    | D8  | 1   | 1 | C8  | LA17  |

| DRQ0      | D9  | 1   | 1 | C9  | -MEMR |

| -DACK5    | D10 | 1   | 1 | C10 | -MEMW |

| DRQ5      | D11 | 1   | 1 | C11 | SD08  |

| -DACK6    | D12 | 1   | 1 | C12 | SD09  |

| DRQ6      | D13 | 11  | 1 | C13 | SD10  |

| - DACK7   | D14 | 1 - | 1 | C14 | SD11  |

| DRQ7      | D15 | 1   | 1 | C15 | SD12  |

| +5Vdc     | D16 | 1   | 1 | C16 | SD13  |

| -MASTER   | D17 | 1   | 1 | C17 | SD14  |

| GND       | D18 | L   | 1 | C18 | SD15  |

|           |     |     |   | 1   |       |

I/O CHANNEL J2 – J7

### SYSTEM INTERRUPTS

Sixteen levels of system intrrupts are provided by the 80286 NMI and two 8259A Interrupt Controller chips. The following shows the interrupt-level assignments in decreasing Priority:

| LEVEL                                                              | FUNCTION                                                                                                                                      |

|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Microprocessor NMI<br>Interrupt controllers<br>CTLR 1 CTLR 2       | Parity or I/O channel check                                                                                                                   |

| IRQ 0<br>IRQ 1<br>IRQ 2                                            | Timer output 0<br>Keyboard (Output buffer full)<br>Interrupt from CTLR 2                                                                      |

| IRQ8<br>IRQ9<br>IRQ10<br>IRQ11<br>IRQ12<br>IRQ13<br>IRQ14<br>IRQ15 | Realtime clock interrupt<br>Software redirected to INT OAh (IRQ2)<br>Reserved<br>Reserved<br>Coprocessor<br>Fixed disk controller<br>Reserved |

| IRQ 3<br>IRQ 4<br>IRQ 5<br>IRQ 6<br>IRQ 7                          | Serial port 2<br>Serial port 1<br>Parallel port 2<br>Diskette controller<br>Parallel port 1                                                   |

### DIRECT MEMORY ACCESS

Eight DMA channels are supported by the system. Two Intel 8237-5 DMA controller chips (four channels in each chip) are used. DMA channels are assigned as follows:

| CTLR1           | CTLR2                     |

|-----------------|---------------------------|

| Ch 0 – Spare    | Ch 4 — Cascade for CTRL 1 |

| Ch 1 – SDLC     | Ch 5 — Spare              |

| Ch 2 – Diskette | Ch 6 — Spare              |

| Ch 3 – Spare    | Ch 7 — Spare              |

Channels 0 through 3 are contained in DMA controller 1. Transfers of 8-bit data, 8-bit I/O adapters and 8-bit or 16-bit system memory are supported by these channels. Each of these channels will transfer data in 64KB blicks throughout the 16-megabyte system address space.

Channel 4 through 7 are contained in DMA conroller 2. To cascade channels 0 through 3 to the microprocessor, use channel 4. Transfers of 16-bit data between 16-bit adapters and 16-bit system memory are supported by channels 5, 6, 7. DMA channels 5 through 7 will transfer data in 128KB blocks throughout the 16-megabyte system address space. These channels will not transfer data on odd-byte boundaries.

The addresses for the page register are as follows:

17

| PAGE REGISTER                                                                                                                  | I/O HEX ADDRESS                                              |

|--------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| DMA channel 0<br>DMA channel 1<br>DMA channel 2<br>DMA channel 3<br>DMA channel 5<br>DMA channel 6<br>DMA channel 7<br>Refresh | 0087<br>0083<br>0081<br>0082<br>008B<br>0089<br>008A<br>008F |

Address generation for the DMA channels is as follows:

\* For DMA channels 3 through 0

| SOURCE  | DMA PAGE REGISTERS | 8237A-5  |

|---------|--------------------|----------|

| Address | A23 - A16          | A15 – A0 |

- Note: To generate the addressing signal "byte high enable" (BHE) invert address line A0.

- \* For DMA channels 7 through 5

| SOURCE  | DMA PAGE REGISTERS | 8237A- 5 |

|---------|--------------------|----------|

| Address | A23 – A17          | A16 – A1 |

Note: The BHE and A0 addressing signals are forced to a logic 0. DMA channel addresses do not increase or decrease through page boundaries (64KB for channels 0 throught 3 and 128KB for channels 5 through 7).

# REAL TIME CLOCK AND NONVOLATILE RAM

The real time clock MC146818 and its 64 bytes of RAM information are backed up by 6V DC battery. the internal colock circuitry uses 14 bytes while the rest is allocated to system configuration.

| ADDRESS | DESCRIPTION                             |

|---------|-----------------------------------------|

| 00      | Seconds                                 |

| 01      | Second alarm                            |

| 02      | Minutes                                 |

| 03      | Minute alarm                            |

| 04      | Hours                                   |

| 05      | Hour alarm                              |

| 06      | Day of week                             |

| 07      | Date of month                           |

| 08      | Month                                   |

| 09      | Year                                    |

| 0A      | Status register A                       |

| OB      | Status register B                       |

| 0C      | Status register C                       |

| 0D      | Status register D                       |

| 0E      | Diagnostic status byte                  |

| OF      | Shutdown                                |

| 10      | Diskette drive type byte-driver A and B |

| 11      | Reserved                                |

| 12      | Fixed disk type byte – driver C and D   |

| 13      | Reserved                                |

| 14      | Equipment byte                          |

| 15      | Low base memory                         |

| 16      | High base memory                        |

| 17      | Low expansion memory byte               |

| 18      | High expansion memory byte              |

#### DESCRIPTION ADDRESS 19 – 2D Reserved 2 byte CMOS checksum 2E - 2FLow expansion memory byte 30 High expansion memory byte 31 Data century byte 32 Information flags (set during power on) 33 Reserved $\cdot 34 - 3F$

#### ATTACHMENT I FUNCTION OF JUMPER JP13/JP14/ JP15/JP18

In this mother board, Jumper setting of JP13/JP14/JP15/ JP18 is provide to enable user to change speed via software. As different ''BIOS'' and ''keyboard controller'' makes different Jumper setting of JP13/JP14/JP15/JP18. Before you choose the specific ''BIOS'' for this mother board, be sure that the keyboard controller (8042 controller) is compatible with this ''BIOS''.

Once the "BIOS" and "Keyboard controller" are selected, it is necessary to short one of these Jumper JP13/JP14/ JP15/JP18 for software speed change, and which according to the "controller pin" that this specific "BIOS" and "keyboard controller" supported.

a) Short JP13: menas keyboard controller is set on "PIN 30"

b) Short JP14: means keyboard controller is set on "PIN 23"

c) Short JP15: means keyboard controller is set on "PIN 27"

d) Short JP18: means keyboard controller is set on "PIN 32"

While the Jumpers JP13/JP14/JP15/JP18 is set correctly, you can change the system speed by software.