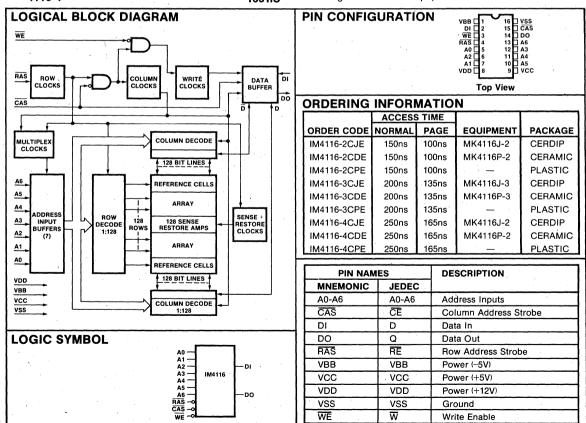

# IM4116/MK4116 16,384 Bit NMOS Dynamic RAM

### FEATURES

- Industry Standard 16-pin configuration

- Standard 10% Supplies (+12V, +5V, -5)

- Low Capacitance TTL Compatible Inputs

- TTL Compatible 3-State Outputs Controlled by CAS

- On-chip Address and Data Latches

- Common I/O Capability Using "Early Write" Cycle

Read-Modify-Write, RAS-only Refresh, Page Mode

- Operation

- 128-Cycle RAS-Only Refresh

- Compatible with MOSTEK MK4116

- Read Access

| 4116-2           | 150 nS |

|------------------|--------|

| 4116-3           | 200 nS |

| 4116-4           | 250 nS |

| Page Mode Access |        |

| 4116-2           | 100 nS |

| 4116-3           | 135 nS |

| 4116-4           | 165 nS |

|                  |        |

### **GENERAL DESCRIPTION**

The Intersil IM4116/MK4116 is a 16,384-bit dynamic random access memory employing the latest advances in N-channel silicon-gate MOS technology. The use of double-level poly allows the highest possible density consistent with reliability, high performance and low cost.

The basic memory element is a single transistor which stores charge on a small capacitor. These dynamic memory "cells" are organized into an array of 128 rows by 128 columns. Each of the 128 rows requires refreshing at least every two milliseconds. This refresh may be accomplished on a given row by any read or  $\overline{RAS}$ -only cycle. A page-mode feature is included which reduces access and/or cycle time when multiple operations are performed within the same row.

All inputs and outputs are TTL compatible. On-chip address registers and three-state outputs simplify system design and allow for interfacing with common bus structures.

The device is packaged in a standard 16-pin DIP, providing high system bit density and compatibility with automatic testing and insertion equipment.

### **ABSOLUTE MAXIMUM RATINGS**<sup>1</sup>

| SYMBOL | DESCRIPTION                        | MIN  | MAX  | UNITS | NOTES |

|--------|------------------------------------|------|------|-------|-------|

| VIN    | Voltage on any Pin Relative to VBB | -0.5 | +20  | ۰. V  | 2, 3  |

| PD     | Power Dissipation                  |      | 1    | W     |       |

| IOS    | Short Circuit Output Current       |      | 50   | mA    |       |

| TSTORE | Storage Temperature                | -55  | +150 | °C    | 1     |

| . TA   | Ambient Temperature Under Bias     | 0    | +70  | °C    |       |

#### NOTES:

- 1. Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Functional operation of the device at these or any other conditions exceeding those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect device reliability. 2

- $VSS VBB \ge 4.5V$

- This device contains internal circuitry to protect against damage due to static charge. Conventional precautions should be observed, 3. however, during storage, handling, and use to avoid exposure to excessive voltages.

### **OPERATING CONDITIONS<sup>1</sup>**

| SYMBOL | DESCRIPTION                    | MIN  | MAX  | UNITS |

|--------|--------------------------------|------|------|-------|

| VBB    | VBB Supply                     | -4.5 | -5.5 | V     |

| VCC    | VCC Supply                     | 4.5  | 5.5  | V     |

| VDD    | VDD Supply                     | 10.8 | 13.2 | V     |

| VSS    | VSS Supply                     | 0    | 0    | V     |

| TA     | Ambient Temperature Under Bias | 0    | +70  | °C    |

NOTE: VBB must be applied prior to and removed after other supply voltages.

#### ELECTRICAL PARAMETERS VDD = +12V ± 10%, VCC = +5V ± 10%, VSS = 0V, VBB = -5V ± 10%, TA = 0°C to +70°C

| SYMBOL       | DESCRIPTION                                | MIN     | МАХ   | UNITS | NOTES           |

|--------------|--------------------------------------------|---------|-------|-------|-----------------|

| IDD1         | Average Operating Supply Currents          |         | 35    | mA    | ·               |

| ICC1<br>IBB1 | (RAS, CAS cycling; tRC = tRC (min))        |         | 200   | μA    | 1               |

| IDD2         | Standby Supply Current                     |         | 1.5   | mA    |                 |

| ICC2         | $(\overline{RAS} = VIHC)$                  | -10     | 10    | μA    |                 |

| IBB2         |                                            |         | 100   | μΑ    | Also in the     |

| IDD3         | Average Refresh Supply Currents            | · · · · | 27    | mA    |                 |

| ICC3         | (RAS Cycling, CAS = VIHC; tRC = tRC (Min)) | -10     | 10    | μĂ    |                 |

| IBB3         |                                            |         | 200   | μA    |                 |

| IDD4         | Average Page Mode Supply Current           |         | 27    | mA    |                 |

| ICC4         | (RAS = VIL, CAS cycling; tPC = tPC (min))  |         |       |       | -4 + <b>1</b> , |

| IBB4         |                                            | 1       | 200   | μA    |                 |

| VIH          | Input HIGH Voltage (A, DI)                 | 2.4     | 7.0 / | V     |                 |

| VIH1         | Input HIGH Voltage (RAS, CAS, WE)          | 2.7     | 2.7   | v     |                 |

| VIL          | Input LOW Voltage                          | -1.0    | +0.8  | V     |                 |

| IIL          | Input Leakage Current                      | -10     | +10   | μΑ    |                 |

| VOH          | Output HIGH Voltage                        | 2.4     | 9     | V ·   |                 |

| VOL          | Output LOW Voltage                         |         | 0.4   | V .   |                 |

| IOZ          | Output Leakage Current                     | -10     | +10   | μΑ    | 3, 4            |

| CIN          | Input Capacitance (A)                      |         | 5     | pF    | 2               |

| CIN1         | Input Capacitance (RAS, CAS, DI, WE)       |         | 10    | pF    | 2<br>2          |

| CO CO        | Output Capacitance (DO)                    |         | 7     | pF    | 2               |

NOTES: 1. ICC1 and ICC4 depend upon output loading.

2. These parameters characterized and periodically sampled; not 100% tested.

**3.**  $0V \le V_{OUT} \le 10V$

4.  $\overline{RAS} = \overline{CAS} = V_{IH}$

**TIMING PARAMETERS**1, 2, 3 VDD = +12V ± 10%, VCC = +5V ± 10%, VSS = 0V, VBB = -5V ± 10%, TA = 0°C to +70°C

| SYMBOL   |                 |                                                 | MK4116-2 MK4116-3 |       |     | 116-3 | -3 MK4116-4 |       |       |       |

|----------|-----------------|-------------------------------------------------|-------------------|-------|-----|-------|-------------|-------|-------|-------|

| MNEMONIC | JEDEC8          | DESCRIPTION                                     | MIN               | MAX   | MIN | MAX   | MIN         | MAX   | UNITS | NOTES |

| tAR      | TRELAX (C)      | RAS LOW to Column Address Hold Time             | 95                |       | 120 | 1     | 160         |       |       |       |

| tASC     | TAVCEL          | Column Address Set-up Time                      | -10               |       | -10 |       | -10         |       |       |       |

| tASR     | TAVREL          | Row Address Set-up Time                         | 0                 |       | :0  |       | 0           |       | 1.1   |       |

| tCAC     | TCELQV          | Access Time from CAS                            |                   | 100   | 1.1 | 135   |             | 165   |       | 4     |

| tCAH     | TCELAX          | CAS LOW to Column Address Hold Time             | 45                | 1.1   | 55  |       | . 75        |       | · · · |       |

| tCAS     | TCELCEH         | CAS Pulse Width                                 | 100               | 10000 | 135 | 10000 | 165         | 10000 |       |       |

| tCP      | TCEHCEL         | Page Mode CAS Precharge Time                    | 60                |       | 80  |       | 100         |       |       |       |

| tCRP .   | TCEHREL         | CAS to RAS Precharge Time                       | -20               |       | -20 |       | -20         |       | 1     |       |

| tCSH     | TRELCEH         | RAS LOW to CAS HIGH Delay                       | 150               | [     | 200 |       | 250         |       | I     |       |

| tCWD     | TCELWL          | CAS LOW to WE LOW Delay                         | 70                |       | 95  |       | 125         |       | 1 1 1 | 5     |

| tCWL     | TWLCEH          | WE LOW to CAS HIGH Set-up Time                  | 60                |       | 80  |       | 100         |       | 1.    |       |

| tDH      | TCELDX or TWLDX | CAS LOW or WE LOW to Data In Valid Hold Time    | 45                | N     | 55  |       | 75          |       | nS    | 6     |

| tDHR     | TRELDX          | RAS LOW to Data In Valid Hold Time              | 95                |       | 120 |       | 160         |       |       |       |

| tDS      | TDVCEL or TDVWL | Data In Stable to CAS LOW or WE LOW Set-up Time | 0                 |       | 0   |       | · 0 ·       |       | 1.    | 6     |

| tOFF     | TCEHQZ          | CAS HIGH to Output OFF Delay                    | 0                 | 40    | 0   | 50    | 0           | 60    |       |       |

| tPC      | TCELCEL (P)     | Page Mode Cycle Time                            | 170               |       | 225 |       | 275         |       | 1     |       |

| tRAC     | TRELOV          | Access Time from RAS                            |                   | 150   |     | 200   |             | 250   | 1     | 4     |

| tRAH     | TRELAX (R)      | RAS LOW to Row Address Hold Time                | -20               |       | 25  |       | 35          |       | 1     |       |

| tRAS     | TRELREH         | RAS Pulse Width                                 | 150               | 10000 | 200 | 10000 | 250         | 10000 |       |       |

| tRC      | TRELREL         | Random Read or Write Cycle Time                 | 375               |       | 375 | 1     | 410         |       |       |       |

| tRCD     | TRELCEL         | RAS LOW to CAS LOW Delay                        | 20                | 50    | 25  | 65    | 35          | 85    | 1     | 7.    |

| tRCH     | TCEHWX          | Read Hold Time                                  | 0                 |       | 0   |       | 0           |       | 1 .   |       |

| tRCS     | TWHCEL          | Read Set-up Time                                | 0                 |       | 0   |       | 0           |       | 1     |       |

| tREF     |                 | Refresh Interval                                | 1                 | 2     |     | 2     |             | 2 .   | mS    |       |

| tRMW     | TRELREL (RMW)   | Read-Modify-Write Cycle Time                    |                   |       |     |       |             |       |       |       |

| tRP      | TREHREL         | RAS Precharge Time                              | 100               |       | 120 |       | 150         |       | 1     |       |

| tRSH     | TCELREH         | CAS LOW to RAS HIGH Delay                       | 100               | 1     | 135 |       | 165         |       |       |       |

| tRWC     | TRELREL (R/W)   | Read/Write Cycle Time                           | 375               | 1.    | 375 |       | 515         |       | ] · · |       |

| tRWD     | TRELWL          | RAS LOW to WE LOW Delay                         | 120               | 1     | 160 |       | 200         |       | nS    |       |

| tRWL     | TWLREH          | WE LOW to RAS HIGH Set-up Time                  | 60                | 1     | 80  | 1     | 100         | 1     | 1     | ·     |

| tT       |                 | Transition Time                                 | 3                 | 35    | 3   | 50    | 3           | 50    | ]     | 3     |

| tWCH     | TCELWH          | Write Hold Time                                 | 45                |       | 55  |       | 75          |       | ]     |       |

| tWCR     | TRELWH          | RAS LOW to Write Hold Time                      | 95                |       | 120 |       | 160         |       | ] .   |       |

| tWCS     | TWLCEL          | WE LOW to CAS LOW Set-up Time                   | -20               |       | -20 | 1     | -20         |       | ]     | 5     |

| tWP      | TWLWH           | Write Pulse Width                               | 45                | 1     | 55  | 1     | 75          | 1     | 1     |       |

NOTES: 1. Several cycles are required after power-up before proper device operation is achieved. Any eight cycles which perform refresh are adequate for this purpose.

- 2. Unless otherwise noted, tRISE = tFALL = 5nS

- 3. VIHC (min), VIH (min) and VIL (max) are reference levels for timing measurements.

- 4. Loading equivalent to two TTL inputs +100 pF

- 5. tWCS, tCWD, and tRWD are not restrictive operating parameters. They are included in the datasheet as electrical characteristics only: for tWCS ≥ TWCS (min), the cycle is an early-write cycle and the data output will remain high-impedance throughout the entire cycle; for tCWD > tCWD (min) and tRWD ≥ tRWD (min), the cycle is a read-write cycle and the data output will contain data read from the selected cell; if neither of the above sets of conditions is satisfied, the condition of the data output (at access time) is indeterminate.

- 6. For positive tWCS these parameters are referenced to CAS. For negative tWCS, or read-write cycles these parameters are referenced to WE.

- 7. For tRCD  $\geq$  tRCD (max), access time is controlled by tCAC.

### FUNCTIONAL DESCRIPTION

## INNERSIL

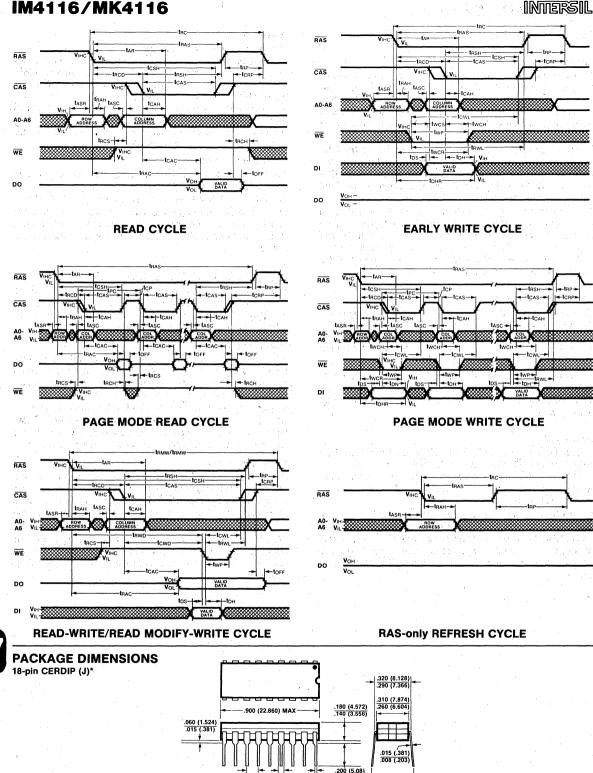

#### Addressing

Fourteen address bits are required to select one of the 4116's 16,384 possible bit locations. These 14 address bits are latched on-chip in two groups of seven bits. The Row Address Strobe ( $\overline{RAS}$ ) latches the 7-bit row address on its falling edge; similarly, the 7-bit column address is latched by  $\overline{CAS}$ .

The normal sequence of events is as follows: First, the 7-bit row address is applied to the address inputs. At the end of the row address setup time (tASR),  $\overrightarrow{RAS}$  is brought LOW. After the row address hold time (tRAH) has elapsed, the 7-bit column address is applied and  $\overrightarrow{CAS}$  is brought LOW.

The column address information is not used internally until tRCD (max) after RAS-falls. Further, CAS, is gated with the RAS clock generator such that it may occur at any time from tRCD (min) to tRCD (max), without effecting access time. If CAS occurs after tRCD (max) the access time will be lengthened by the delay from tRCD (max) to CAS.

#### Page Mode Operation

Successive memory cycles accessing the same row in the memory array require the row address and  $\overline{\text{RAS}}$  to be supplied only once. Further accesses to the same row require only column addresses and  $\overline{\text{CAS}}$ , with  $\overline{\text{RAS}}$  held LOW.

In addition to savings in access and cycle time, page mode operation results in reduced power consumption since dynamic power due to RAS transitions is drawn only once per row address.

#### Data Input

Data to be written is strobed into the on-chip data latch by a combination of  $\overrightarrow{CAS}$  and  $\overrightarrow{WE}$  while  $\overrightarrow{RAS}$  is active. Whichever of  $\overrightarrow{CAS}$  and  $\overrightarrow{WE}$  makes the later negative-going transition serves as the data strobe. Several different write cycles are made possible by this flexibility.

An "early-write" cycle takes place if  $\overline{WE}$  goes LOW before CAS. In the case where data-in (DI) is not valid when CAS goes LOW,  $\overline{WE}$  must be delayed until after CAS falls. In this "delayed-write" cycle, data setup and hold times are referenced to the negative-going edge of  $\overline{WE}$ , rather than CAS.

#### Data Output.

The data output (DO) unconditionally assumes the highimpedance state wherever CAS is HIGH. For read, readmodify-write, or delayed-write cycles, DO remains highimpedance until access time, at which time it will reflect the logic state of the addressed cell. DO remains highimpedance in an early-write cycle, or in cycles where RAS and CAS are not both received. Thus, in systems which utilize early-write cycles exclusively, DI, and DO may be connected together with no conflict.

#### Input/Output Levels

All inputs, including RAS and CAS, are low-capacitance high-impedance, and TTL-level compatible. Special clock drivers are not required, simplifying input driver design.

In order to prevent ringing, signal termination resistors are usually necessary. In general, transmission line techniques must be utilized on signal lines to achieve maximum system speeds.

#### Refresh

Any cycle in which  $\overline{\text{RAS}}$  occurs serves to refresh the selected row. However, it is generally more convenient (and requires substantially less power) to perform the refresh operation using the  $\overline{\text{RAS}}$ -only cycle. Each of the 128 rows must be refreshed at least once per two milliseconds.

#### **Power Sequencing**

VBB should be applied before and removed after other supply voltages. Under system failure conditions in which one or more supplies exceed the specified limit, significant additional margin against catastrophic device failure may be achieved by forcing RAS and CAS to the inactive state.

After power is applied, the MK4116 requires several cycles before proper device operation is achieved. Any eight cycles which perform refresh are adequate for this purpose.

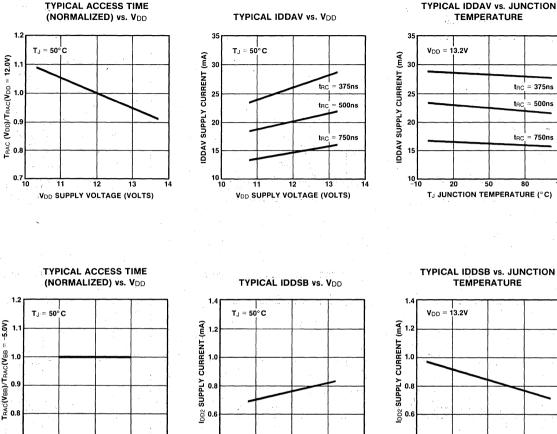

#### **Power Dissipation**

Because of the extensive use of dynamic circuitry in the MK4116, most of the dissipated power is as a result of a transition on RAS or CAS. Thus, the dynamic power is primarily a function of operating frequency. Worst case power dissipation is 462 MW at 375nS cycle time.

VCC is utilized only to power the output buffer, and is not connected elsewhere; ICC, is thus a function only of output loading. VCC may be left unconnected for battery-backup operation.

<u>.110 (2.794)</u> <u>.070 (1.778)</u> <u>.023 (.584)</u> <u>.125 (3.175)</u> <u>.090 (2.286)</u> <u>.030 (.762)</u> <u>.015 (.381)</u>

.400 (10.16)

\*Hermetic: Maximum leakage rate 5 x 10-7 atm. cc/sec.

## **TYPICAL CHARACTERISTICS**

t<sub>RC</sub> = 375ns

t<sub>RC</sub> = 750ns

80

110

tRC = 500ns

0.4 L 10

11

-6.0

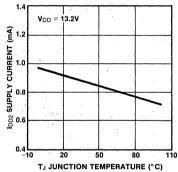

#### TYPICAL IDDSB vs. JUNCTION TEMPERATURE

50

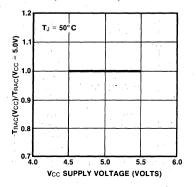

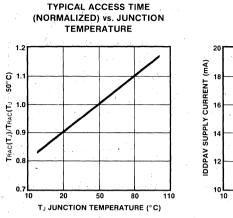

**TYPICAL ACCESS TIME** (NORMALIZED) vs. VCC

-5.0

VBB SUPPLY VOLTAGE (VOLTS)

-5.5

0.7

-4.0

-4.5

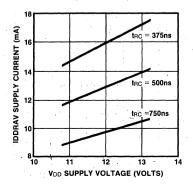

TYPICAL IDDRAV vs. VDD

12

VDD SUPPLY VOLTAGE (VOLTS)

13

14

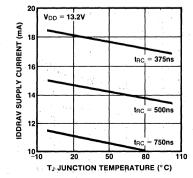

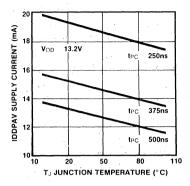

**TYPICAL IDDRAV vs. JUNCTION** TEMPERATURE

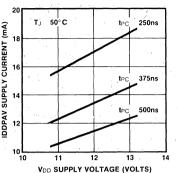

TYPICAL IDDPAV vs. VDD

#### TYPICAL IDDPAV vs. JUNCTION TEMPERATURE

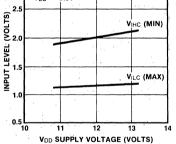

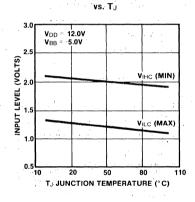

TYPICAL CLOCK INPUT LEVELS vs. VDD

3.0

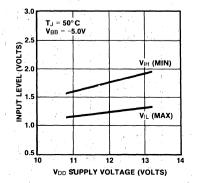

T\_J = 50° C VBB = -5.0V

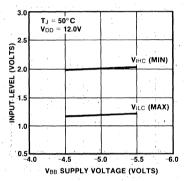

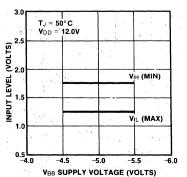

TYPICAL CLOCK INPUT LEVELS vs. V<sub>BB</sub>

TYPICAL CLOCK INPUT LEVELS

#### TYPICAL ADDRESS AND DATA INPUT LEVELS vs. VDD

TYPICAL ADDRESS AND DATA INPUT LEVELS vs. V<sub>BB</sub>

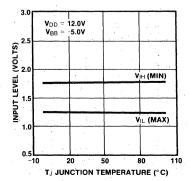

TYPICAL ADDRESS AND DATA INPUT LEVELS vs. TJ

7-26

### SYMBOLS AND ABBREVIATIONS

This data sheet utilizes a new set of specification nomenclature. This new format is an IEEE and JEDEC supported standard for semiconductor memories. It is intended to clarify the symbols, abbreviations and definitions, and to make all memory data sheets consistent. We believe, once acclimated, you will find this standardized format easy to read and use.

#### **ELECTRICAL PARAMETER ABBREVIATIONS**

All abbreviations use upper case letters with no subscripts. The initial symbol is one of these four characters:

- V (Voltage)

- I (Current)

- P (Power)

- C (Capacitance)

The second letter specifies input (I) or output (O), and the third letter indicates HIGH (H), LOW (L) or off (Z) state of the pin during measurements. Examples:

VIL — Input Low Voltage IOZ — Output Leakage Current

#### TIMING PARAMETER ABBREVIATIONS

All timing abbreviations use upper case characters with no subscripts. The initial character is always T and is followed by four descriptors. These characters specify two signal points arranged in a "from-to" sequence that define a timing interval. The two descriptors for each signal point specify the signal name and the signal transitions. Thus the format is:

Signal name from which interval is defined Transition direction for first signal Signal name to which interval is defined Transition direction for second signal

Signal Definitions:

- A = Address

- D = Data In

- Q = Data Out

- W = Write Enable

- E = Chip Enable

- S Chip Select

- G Output Enable

Transition Definitions:

- H = Transition to High

- L = Transition to Low

- V = Transition to Valid

- X = Transition to Invalid or Don't Care

- Z = Transition to Off (High Impedance)

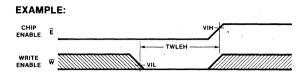

The example shows write-pulse setup time defined as TWLEH-Time from Write enable Low to chip Enable High.

### TIMING LIMITS

The table of timing values shows either a minimum or a maximum limit for each parameter. Input requirements are specified from the external system point of view. Thus, address set-up time is shown as a minimum since the system must supply at least that much time (even though most devices do not require it). On the other hand, responses from the memory are specified from the device point of view. Thus, the access time is shown as a maximum since the device never provides data later than that time.

#### WAVEFORMS

тхххх

| WAVEFORM<br>SYMBOL | INPUT                                  | Ουτρυτ                     |

|--------------------|----------------------------------------|----------------------------|

|                    | MUST BE<br>VALID                       | WILL BE<br>VALID           |

|                    | CHANGE<br>FROM H TO L                  | WILL CHANGE<br>FROM H TO L |

|                    | CHANGE<br>FROM L TO H                  | WILL CHANGE<br>FROM L TO H |

|                    | DON'T CARE:<br>ANY CHANGE<br>PERMITTED | CHANGING:<br>STATE UNKNOWN |

| $\rightarrow$      |                                        | HIGH<br>IMPEDANCE          |