# IBM 64/256KB Memory Expansion Option and 64KB Memory Module Kit

## **Contents**

| Description               |         | 1 |

|---------------------------|---------|---|

|                           | Address |   |

| Operating Characteristics |         | 3 |

| Specifications            |         | 5 |

| Logic Diagrams            |         | 7 |

### **Description**

The 64KB Memory Module Kit and the 64/256KB Memory Expansion Option are available for the IBM Personal Computer family of products. Depending upon the amount of memory currently installed on the system board, memory module kits can be added to provide a maximum of 256KB of RAM without using any of the system unit expansion slots for a memory expansion option. The system board must be populated to the maximum 256KB of RAM before a 64/256KB Memory Expansion Option can be installed.

The IBM 64/256KB Memory Expansion Option has four banks of nine pluggable sockets. Each bank will accept a 64KB Memory Module Kit, consisting of 9 (64K by 1) modules with 16-pin industry-standard parts. The base 64/256K expansion option comes with modules installed in bank 0, providing 64K of memory. The kits must be installed sequentially into banks 1, 2, and 3. The following chart shows how the 64KB Memory Module Kit can be installed on the system board and the 64/256KB Memory Expansion Option.

|                          | Minimum<br>Memory | Maximum<br>Memory | Number of<br>64K Memory<br>Module Kits | Memory<br>Module<br>Type |

|--------------------------|-------------------|-------------------|----------------------------------------|--------------------------|

| 64/256K<br>System Board  | 64K               | 256K              | 1, 2, or 3                             | 64K by 1 Bit,<br>16 pin  |

| 64/256K<br>Memory Option | 64K               | 256K              | 1, 2, or 3                             | 64K by 1 Bit,<br>16 pin  |

In addition to the memory modules, the memory expansion option contains the following circuits: bus buffering, dynamic memory timing generation, address multiplexing, and card-select decode logic.

Dynamic-memory refresh timing and address generation are functions that are performed by the system board and made available in the I/O channel for all devices.

The 64/256KB Memory Expansion Option is parity checked. If a parity error is detected, a latch is set and an I/O 'channel check' line is activated, indicating an error to the microprocessor.

To allow the system unit to address the expanded memory provided by the 64KB Memory Module Kit or the 64/256K Memory Expansion Option, refer to the *Guide to Operations* manual for the proper memory-expansion-option switch settings.

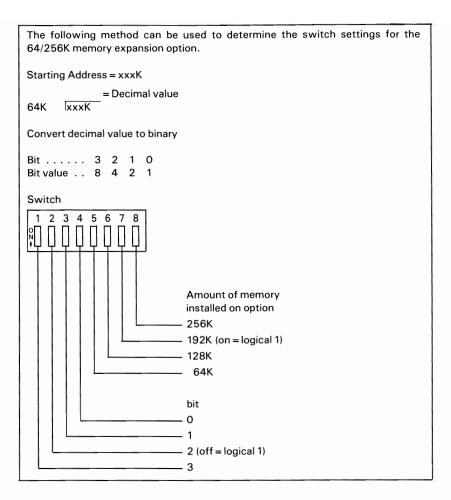

### Switch-Configurable Start Address

The 64/256KB Memory Expansion Option must be configured to reside at a sequential 64K memory address boundary within the system address space. This is done by setting dual-in-line package (DIP) switches on the option. The 64/256KB expansion option has a small DIP module containing eight switches. The switches are used to set the card start address as follows:

| Number | 64/256K Options           |

|--------|---------------------------|

| 1      | ON: A19 = 0; OFF: A19 = 1 |

| 2      | ON: A18 = 0; OFF: A18 = 1 |

| 3      | ON: A17 = 0; OFF: A17 = 1 |

| 4      | ON: A16 = 0; OFF: A16 = 1 |

| 5      | ON: Select 64K            |

| 6      | ON: Select 128K           |

| 7      | ON: Select 192K           |

| 8      | ON: Select 256K           |

#### **DIP Module Start Address**

### **Operating Characteristics**

The system board operates at a frequency of 4.77 MHz, which results in a clock cycle of 210 ns.

Normally four clock cycles are required for a bus cycle so that an 840-ns memory cycle time is achieved. Memory-write and memory-read cycles both take four clock cycles, or 840 ns.

Access and cycle times for memory used on the 64/256 Memory Expansion Option are:

|        | 64K by 1 Bit |

|--------|--------------|

| Access | 200 ns       |

| Cycle  | 345 ns       |

The 64K by 1 modules require only one voltage level of +5 Vdc, and require 128 refresh cycles every 2 ms. Absolute maximum access times are:

|          | 64K by 1 Bit |

|----------|--------------|

| From RAS | 200 ns       |

| From CAS | 115 ns       |

## **Specifications**

| Pin | 64K by 1 Bit Module<br>(used on 64/256K option<br>and 64/256K<br>system board) |

|-----|--------------------------------------------------------------------------------|

| 1   | N/C                                                                            |

| 2   | Data In * *                                                                    |

| 3   | – Write                                                                        |

| 4   | - RAS                                                                          |

| 5   | AO                                                                             |

| 6   | A2                                                                             |

| 7   | A1                                                                             |

| 8   | – 5 Vdc                                                                        |

| 9   | A7                                                                             |

| 10  | A5                                                                             |

| 11  | A4                                                                             |

| 12  | А3                                                                             |

| 13  | A6                                                                             |

| 14  | Data Out * *                                                                   |

| 15  | - CAS                                                                          |

| 16  | GND                                                                            |

| 17  | *                                                                              |

| 18  | *                                                                              |

\*64K by 1 bit modules have 16 pins. \* \*Data In and Data Out are tied together on Data Bits 0-7

(three state bus).

**Memory Module Pin Configuration**

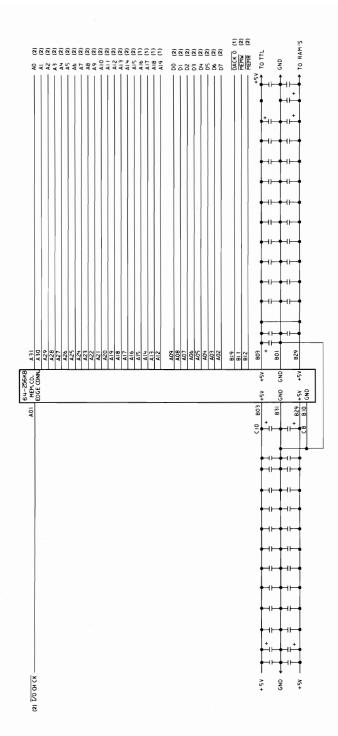

## **Logic Diagrams**

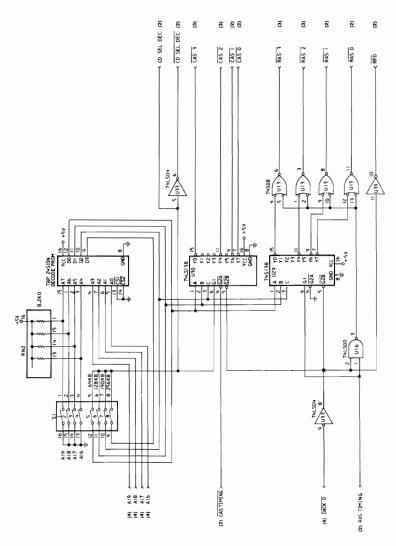

64/256KB Memory Expansion Option (Sheet 1 of 4)

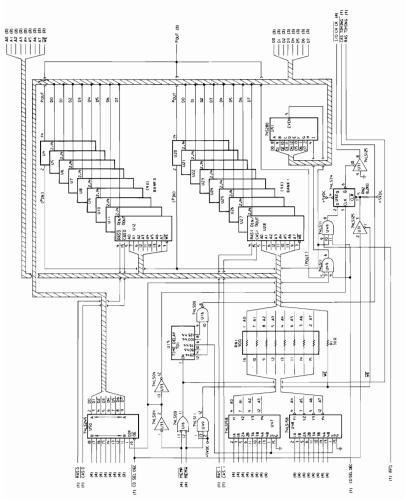

64/256KB Memory Expansion Option (Sheet 2 of 4)

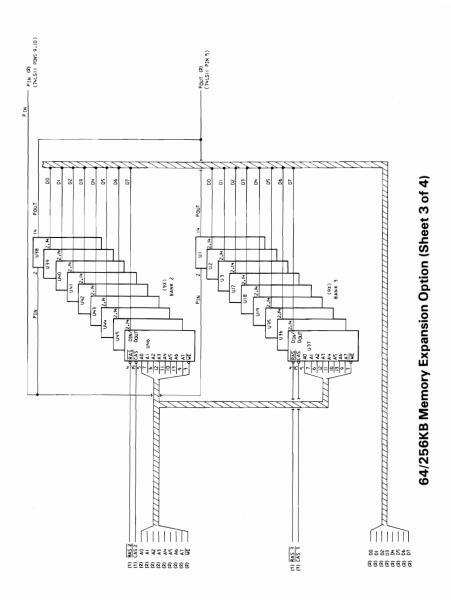

64/256KB Memory Expansion Option (Sheet 4 of 4)