IBM

Personal Computer Hardware Reference Library

# IBM Personal Computer Data Acquisition and Control Adapter Technical Reference

6138163 August 15,1984 © Copyright IBM Corporation 1984

## Contents

| Description 1                          |

|----------------------------------------|

| Major Components 3                     |

| Address Decode and Control Circuitry 4 |

| Data Bus Conversion Circuitry 15       |

| Analog I/O Device 21                   |

| Binary I/O Device 40                   |

| Timer/Counter Device 46                |

| Interrupt Circuitry 54                 |

| Distribution Panel Connector           |

| Expansion Bus 64                       |

| Programming Considerations             |

| Address Decoding 69                    |

| Registers 70                           |

| Device Registers 71                    |

| Timer/Counter Device Registers         |

| Device Number Register                 |

| Interrupt Registers                    |

| Interface                              |

| Distribution Panel Connector           |

| Expansion Bus Connectors               |

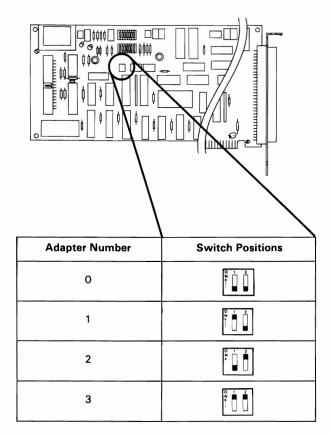

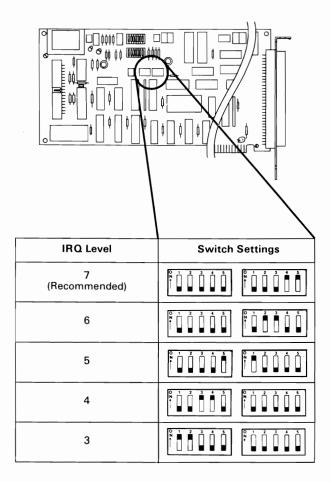

| Switch Settings 101                    |

| Analog Output Range 102                |

| Analog Input Range 106                 |

| Adapter Number 108                     |

| Interrupt Level 109                    |

| Specifications 111                     |

| Data Acquisition Adapter 111           |

| Dimensions 111                         |

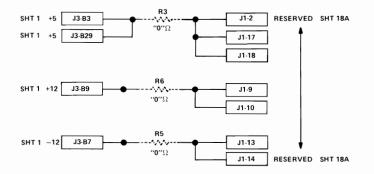

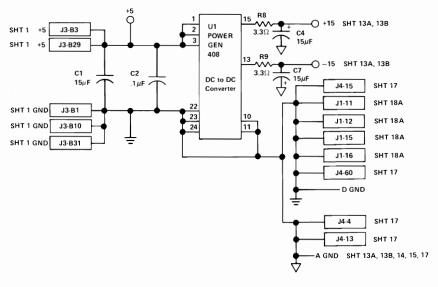

| Power Requirements                     |

| System Reference Voltage               |

| Environment 113                        |

| Data Acquisition Adapter Devices       |

| Analog Output Device                   |

| Analog Input Device                    |

| Binary Device                          |

| 32-Bit Timer Device                    |

| Logic I | Diagrams | • • | • | <br>• | • • | • | • | <br>• | • | • • | • | • | • | <br>• | • | • | <br>• | • | • |    | 123  |

|---------|----------|-----|---|-------|-----|---|---|-------|---|-----|---|---|---|-------|---|---|-------|---|---|----|------|

| Index   |          |     |   |       |     |   |   |       |   |     |   |   |   |       |   |   | <br>  |   | I | nd | ex-1 |

#### August 15, 1984 © Copyright IBM Corporation 1984

## Description

The IBM Personal Computer Data Acquisition and Control Adapter (Data Acquisition Adapter) provides both analog and digital I/O capabilities. It is installed in any full-length expansion slot, and up to four may be installed in a system.

The adapter provides:

- Four analog input channels multiplexed into an analog-to-digital converter (ADC), with 12-bit resolution

- Two analog output channels, each having its own digital-to-analog converter (DAC), with 12-bit resolution

- A 16-bit digital input port

- A 16-bit digital output port

- A 32-bit timer

- A 16-bit, externally-clocked, timer/counter

- An expansion bus.

The Data Acquisition Adapter has a 16-bit data bus and a buffered 8-bit data bus.

The adapter's 16-bit data bus provides access to:

- An analog I/O device:

- Analog input subsystem with four multiplexed channels

- Analog output subsystem with two DACs

- A binary I/O device:

- 16-bit digital input port

- 16-bit digital output port

- Handshaking

- An expansion bus.

The buffered 8-bit data bus provides access to:

- Interrupt circuitry

- A timer/counter device:

- 32-bit timer (Counters 0 and 1)

- 16-bit timer/counter (Counter 2).

Low and high bytes are transferred between the adapter's buffered 8-bit data bus and 16-bit data bus.

A 60-pin, distribution-panel connector is provided for external access to the analog I/O device, the binary I/O device, and the timer/counter device.

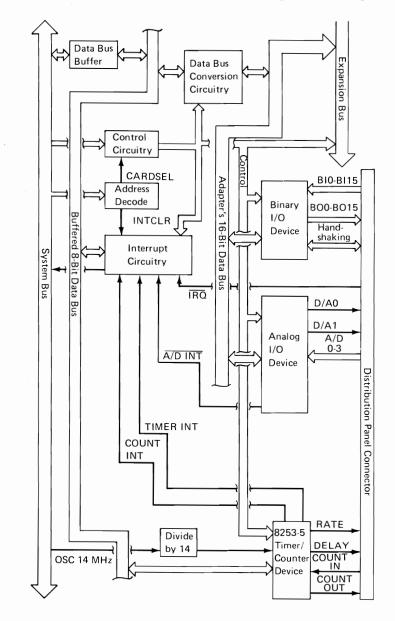

## **Major Components**

Following is a block diagram of the Data Acquisition Adapter.

August 15,1984 © Copyright IBM Corporation 1984 The following are descriptions of the major components shown in the figure on the previous page.

## **Address Decode and Control Circuitry**

The following are descriptions of address decode and control circuitry.

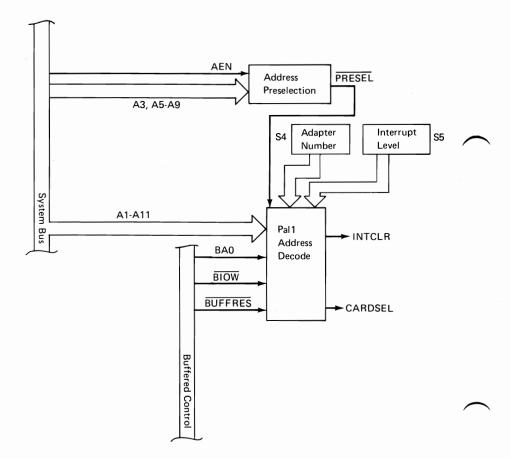

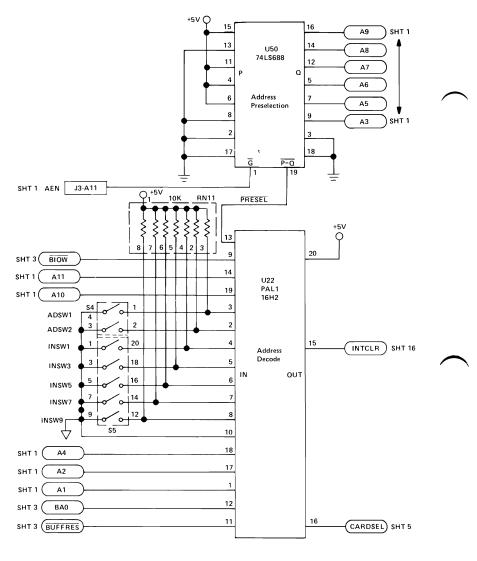

#### **Address Decode**

Following is a block diagram of address decode.

The signals used by the address decode circuitry are:

- AEN Address enable: De-gates the processor and other devices from the I/O channel to allow direct-memory access (DMA) transfers to take place. When active (high), the DMA controller has control of the address bus, data bus, read command lines (memory and I/O), and the write command lines (memory and I/O).

- **PRESEL** Preselect: Indicates preliminary address decoding of the 'address enable' signal (AEN), and the address bits that are common to the adapter's base address and to the shared-interrupt address.

- **CARDSEL** Card select: Indicates communication is in process between the Data Acquisition Adapter and the system. The shared-interrupt re-activation function is not included.

**INTCLR** Shared-interrupt reactivation control signal.

The address preselection circuitry decodes the six address lines, which are common in the adapter address and the shared-interrupt address. AEN is used to prevent false decodes during DMA cycles. Because the adapter has a base address of hex 2E2 through 2E3, and the shared-interrupt address is hex 02Fx (where x is shared-interrupt level 3, 4, 5, 6, or 7), the common address bits are: A9, A7, A6, and A5 equal to 1, and A8 and A3 equal to 0. The resulting signal (PRESEL) indicates that either an adapter access or a shared-interrupt access may be occurring.

The address decode circuitry uses the signals PRESEL, A10, A11, A4, and the signals from the switches S4-1 and S4-2 to decode an adapter's base address. The control decode circuitry uses the resulting signal (CARDSEL) as a master enable and then generates the individual control signals.

When the address decoded is hex 2Fx (where x is the shared interrupt level), INTCLR is generated. INTCLR reactivates the adapter's interrupt circuitry. The address decode circuitry also generates an INTCLR signal at power-on-reset time. Power-on-reset occurs when the 'buffer reset' signal (BUFFRES), which is created by the system bus signal (RESET DRV), goes low.

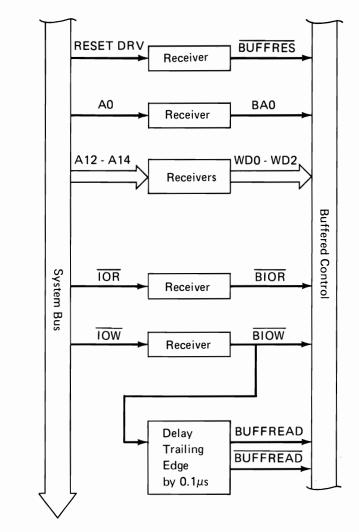

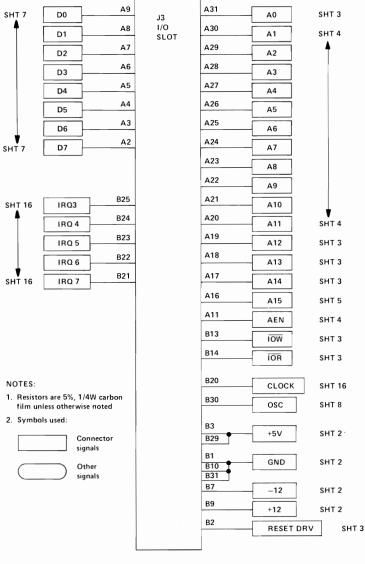

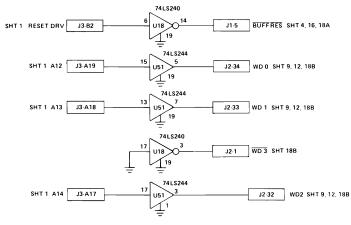

#### System Bus Address and Control Signals

The following is a block diagram of the address and control signals from the system bus.

The address and control signals from the system bus are as follows:

| RESET DRV | Resets system logic upon power-on or<br>during a low line-voltage outage.<br>RESET DRV is synchronized to the falling<br>edge of 'clock' and is active high.                                                                                                       | , |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| BUFFRES   | Buffer reset: Inverse of RESET DRV.<br>Provides power-on-reset of the adapter's<br>control logic. BUFFRES is active low.                                                                                                                                           |   |

| WD0 - WD2 | Word number bits 0 through 2 (system bus<br>address lines A12 through A14 are buffered<br>and renamed WD0 through WD2). Selects<br>word registers 0 through 7 when system bus<br>address line A15 is low. Selects word<br>registers 8 through 15 when A15 is high. |   |

| BA0       | Buffered system-bus address line A0:<br>Selects high or low bytes.                                                                                                                                                                                                 |   |

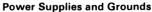

| BIOR      | Buffered I/O read ( $\overline{IOR}$ ): $\overline{BIOR}$ is active<br>low and is used for I/O read operations on<br>the buffered 8-bit data bus.                                                                                                                  |   |

| BIOW      | Buffered I/O write( $\overline{IOW}$ ): $\overline{BIOW}$ is active low and is used for I/O write operations on the buffered 8-bit data bus.                                                                                                                       |   |

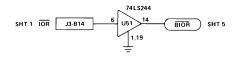

#### **BUFFREAD**

Buffer read: Indicates whether a read or a write operation on the adapter's 16-bit data bus is to be performed. When high, this signal indicates a read operation, and when it is low, a write operation is indicated.

#### **BUFFREAD**

Inverse of BUFFREAD.

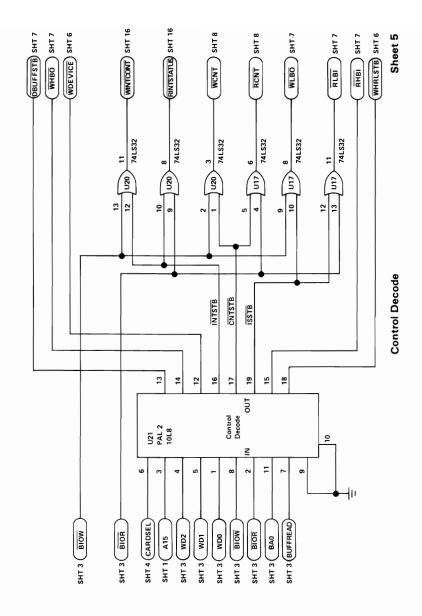

### **Control Decode**

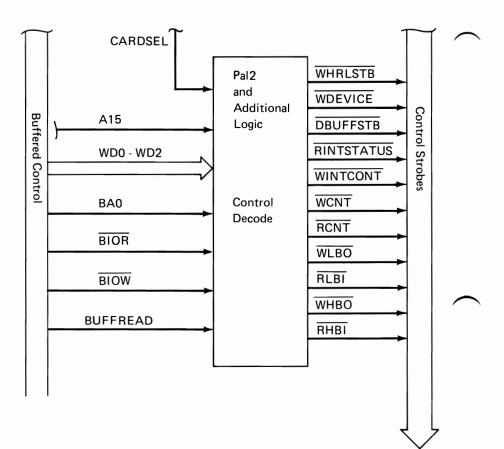

Following is a block diagram of the control decode circuitry.

The control decode circuitry inputs CARDSEL, A15, WD0 through WD2, BA0, BIOR, BIOW, and BUFFREAD generate the following control strobes:

| <br>WHRLSTB  | Write-high read-low strobe: Strobe for<br>reading or writing the data word from the<br>adapter's 16-bit data bus to an on-board or<br>expansion device. |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| WDEVICE      | Write device: Write strobe for the on-board or expansion device number register.                                                                        |

| DBUFFSTB     | Data buffer strobe: Enable strobe for data communications between the system bus and the Data Acquisition Adapter.                                      |

| RINTSTATUS   | Read interrupt status: Read strobe for the interrupt status register.                                                                                   |

| <br>WINTCONT | Write interrupt control: Write strobe for the interrupt status register.                                                                                |

| WCNT         | Write counter: Write strobe for the timer/counter.                                                                                                      |

| RCNT         | Read counter: Read strobe for the timer/counter.                                                                                                        |

| WLBO | Write low byte out: Latch control strobe for latching the low data byte for later transmission to an on-board or expansion device.                                                                                                                                                                  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RLBI | Read low byte in: Enable strobe for reading a data word from an on-board or expansion device to the adapter's 16-bit data bus. The low byte is transmitted to the system bus during this strobe. The high byte is latched during $\overline{\text{RLBI}}$ for later transmission to the system bus. |

| WHBO | Write high byte out: Enable strobe for writing<br>a data word from the adapter's 16-bit data bus<br>to an on-board or expansion device. The low<br>byte is the one previously latched in $\overline{WLBO}$ .<br>The high byte is the current data from the<br>system bus.                           |

| RHBI | Read high byte in: Enable strobe for reading<br>the high byte (previously latched by $\overline{\text{RLBI}}$ )<br>from the adapter's 16-bit data bus to the<br>system bus.                                                                                                                         |

12

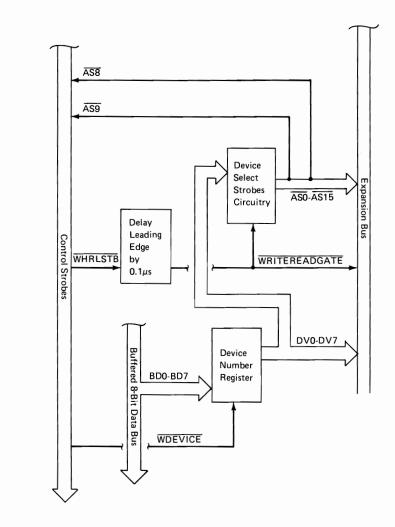

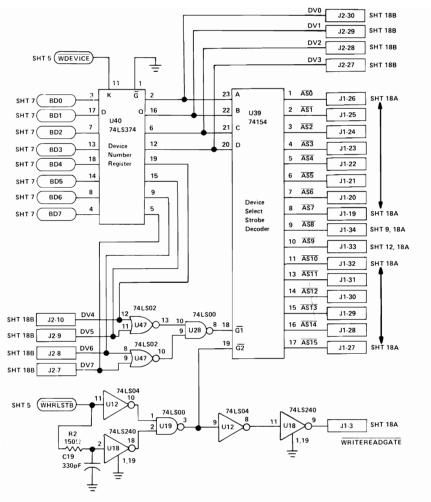

#### **Device Selection**

The following figure shows the device selection circuitry.

The device number register stores the device number. Device strobes are generated for on-board and expansion devices.

The following are used for device selection:

| DV0 - DV7                                                | Device number register bits 0<br>through 7                                                                                                     |

|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| WRITEREADGATE                                            | Strobe for all devices                                                                                                                         |

| $\overline{\text{AS0}}$ through $\overline{\text{AS15}}$ | Strobes for devices 0 through 15:<br>$\overline{AS8}$ selects the binary I/O device,<br>and $\overline{AS9}$ selects the analog I/O<br>device. |

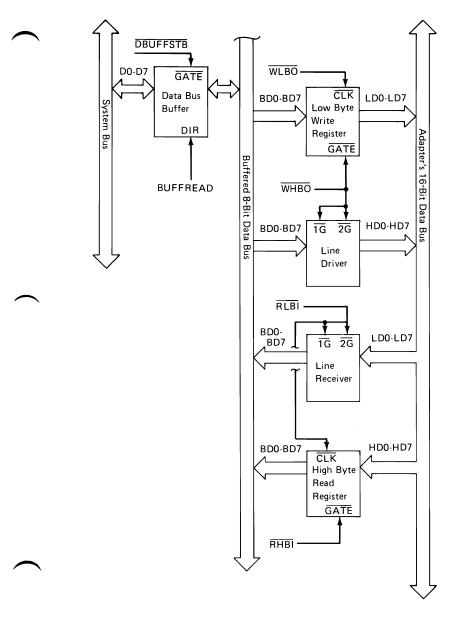

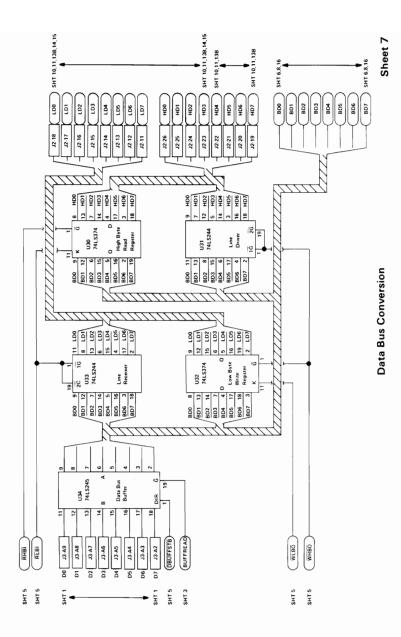

## **Data Bus Conversion Circuitry**

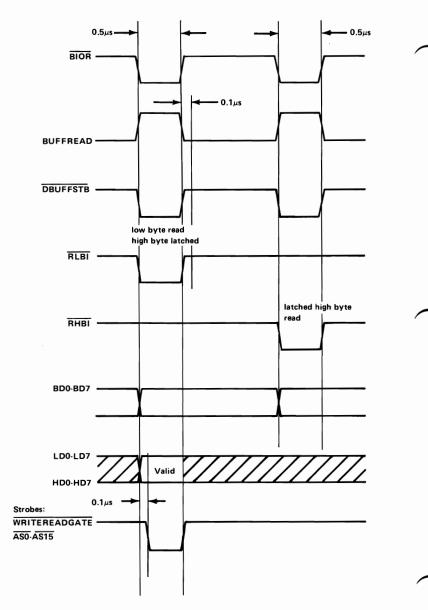

Following is a block diagram of the data bus conversion circuitry.

August 15,1984 © Copyright IBM Corporation 1984

#### **Data Bus Buffer**

The system's data bus (D0 through D7) is buffered by the data bus buffer to create the adapter's buffered data bus (BD0 through BD7). The data bus buffer is activated by  $\overline{\text{DBUFFSTB}}$  during all communications between the system bus and the Data Acquisition Adapter. The data direction is determined by BUFFREAD.

The buffered 8-bit data bus is used for direct 8-bit data communication with the interrupt circuitry, the timer/counter device, and the device number register.

The buffered 8-bit data bus also communicates with the low byte write register, a line driver, a line receiver, and the high byte read register to implement the conversion of the buffered 8-bit data bus into the adapter's 16-bit data bus.

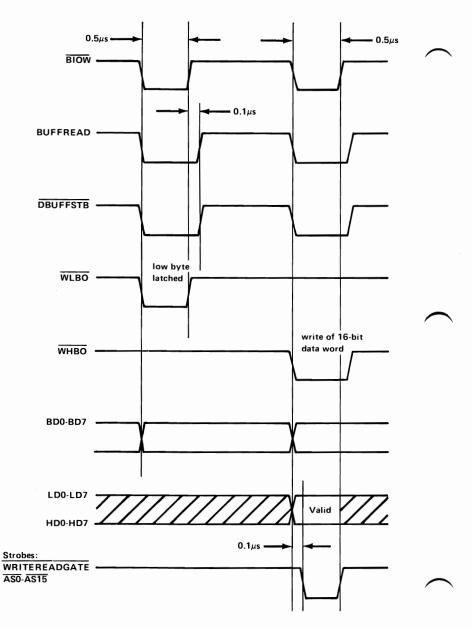

#### Writing Data

Data is written sequentially from the system data bus to the adapter's 16-bit data bus. The low byte is first written to an even address, then the high byte is written to an odd address. The entire 16-bit word is transmitted to an on-board or expansion device at the same time that the high byte is written.

When data is written from the system data bus to an even address (A0 is 0), the  $\overline{WLBO}$  (write low byte out) strobe occurs. The low-byte write register latches the data.

When data is written from the system data bus to an odd address (A0 is 1), the  $\overline{WHBO}$  (write high byte out) strobe occurs. The low-byte write register transmits the previously latched low byte to the adapter's 16-bit data bus LD lines, 0 through 7. At the same time, the line driver transmits the current data on the buffered 8-bit data bus BD lines, 0 through 7, to the adapter's 16-bit data bus HD lines, 0 through 7.

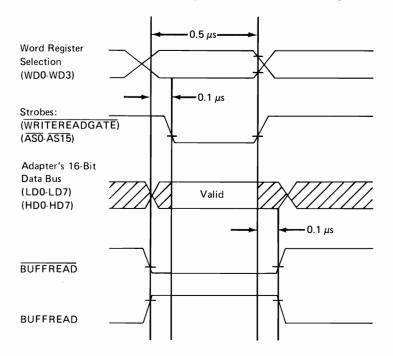

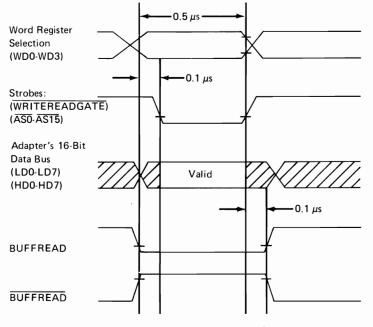

Following is a write timing diagram of the adapter's 16-bit data bus.

#### **Reading Data**

Data is read sequentially from the adapter's 16-bit data bus to the system data bus. The low data byte is first read at an even address, then the high data byte is read at an odd address. The entire 16-bit word is transmitted from an on-board or expansion device at the same time that the low byte is read.

When data is read to the system data bus at an even address (A0 is 0), the  $\overline{\text{RLBI}}$  (read low byte in) strobe occurs. The line receiver transmits the low byte from the adapter's 16-bit data bus LD lines, 0 through 7, to the system data bus. At the same time, the high-byte read register latches the data from the adapter's 16-bit data bus HD lines, 0 through 7.

When data is read from the system data bus at an odd address (A0 is 1), the  $\overline{\text{RHBI}}$  strobe occurs. The high-byte read register transmits the previously latched high byte to the system data bus.

Following is a read timing diagram of the adapter's 16-bit data bus.

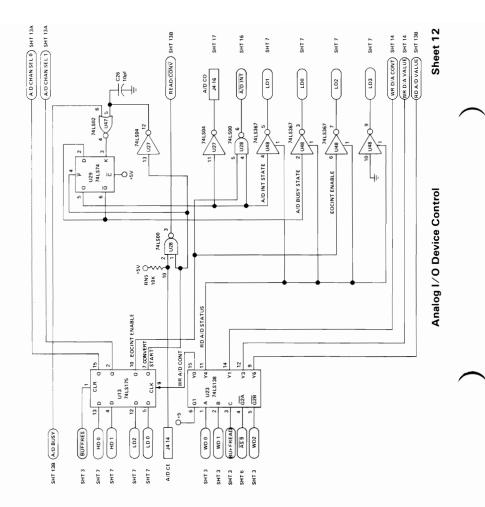

### Analog I/O Device

The Data Acquisition Adapter's analog I/O device consists of two subsystems:

- Analog input: An analog-to-digital conversion subsystem.

- Analog output: A digital-to-analog conversion subsystem.

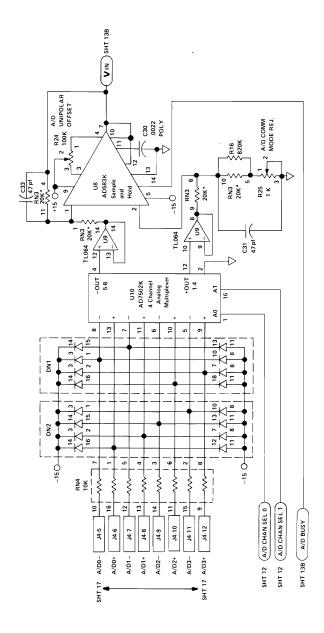

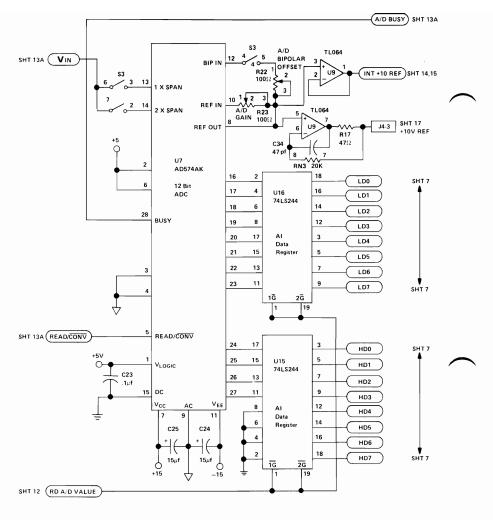

#### **Analog Input Subsystem**

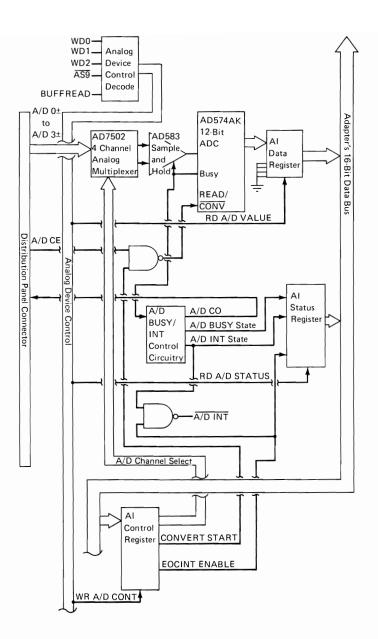

On the following page is a block diagram of the analog input subsystem.

Analog-to-digital conversion is the process of converting analog signals (voltages) over a given range to digital values.

Unlike digital (binary) signals, which have only two voltage states, analog signals have infinite voltage levels over a particular range.

Analog-to-digital converters (ADCs) are categorized by the number of bits of resolution they allow. The greater the number of bits, the greater the number of discrete voltage levels that can be represented.

The Data Acquisition Adapter has an analog input device with the following features:

- Four, multiplexed, differential channels

- An ADC with 12-bit resolution

- Switch-selectable ranges

- Optional data-conversion control with 'A/D convert out' and 'A/D convert enable in' lines.

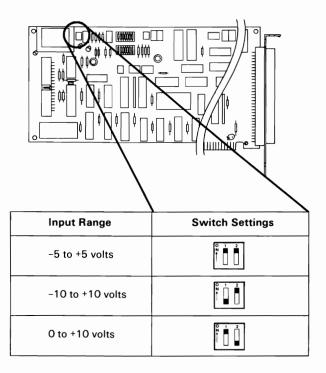

The Data Acquisition Adapter's analog input device (device number 9) has four channels, which are multiplexed into a single ADC. This device converts analog signals in one of three ranges to digital values in the range of 0 to 4095.

The three switch-selectable ranges are:

- - 5 to +5 volts

- -10 to +10 volts

- 0 to +10 volts

The relationship of the analog input voltage to the returned digital value depends on the range for which the hardware is configured. The selected range setting for analog input is in effect for all analog input channels. For example, in the -5 to +5 volt configuration, an input of +4.997 volts generates a full-scale value of 4095; an input of 0 volts generates a value of 2048; and an input of -5 volts generates a value of 0.

#### **Analog Input Device Control**

The use of the  $\overline{AS9}$  strobe causes the analog input device to be accessed as device number 9.

The control decode circuitry of the analog device decodes WD0 through WD2,  $\overline{AS9}$ , and BUFFREAD to generate the following control signals:

| WR A/D CONT   | Write analog-to-digital control.<br>Allows the AI control register to be<br>written to. |

|---------------|-----------------------------------------------------------------------------------------|

| RD A/D STATUS | Read analog-to-digital status. Allows reading of the AI status register.                |

| RD A/D VALUE  | Read analog-to-digital value. Allows reading of the AI data register.                   |

#### **Analog Input Device Registers**

| AI Control Register | The AI control register contains the<br>analog-to-digital channel selection,<br>analog-to-digital interrupt-enable<br>information, and convert start bit<br>information. The AI control register is<br>cleared by BUFFRES during<br>power-on- reset. |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AI Status Register  | The AI status register contains<br>information about 'A/D busy,' the<br>'A/D interrupt status,' and the<br>readback of the 'A/D interrupt enable.                                                                                                    |

| AI Data Register    | The 16-bit AI data register contains<br>the data from the ADC. Because the<br>output of the ADC is a 12-bit digital<br>value, the four highest bits of the<br>register are grounded.                                                                 |

/

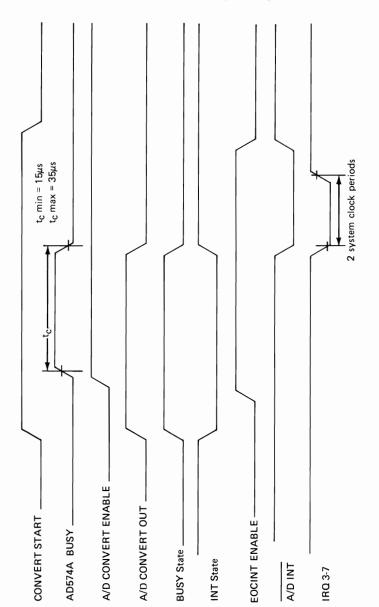

### Following is a timing diagram of analog-to-digital conversion.

#### Starting an Analog-to-Digital Conversion

The convert start bit from the AI control register is logically ANDed with the external 'A/D convert enable' signal from the distribution panel connector. The result is inverted to generate an active low signal, which is brought to the READ/ $\overline{\text{CONV}}$  pin of the AD574 ADC.

#### Reading an Analog-to-Digital Value

The READ/ $\overline{\text{CONV}}$  pin must be taken high before the analog-to-digital value can be read. This is accomplished by writing a convert start bit equal to 0 to the AI control register.

#### **Channel Selection**

The differential analog to digital channel pair is selected by the AD7502 4-channel, analog multiplexer on the basis of the analog-to-digital channel-select bits of the AI control register.

#### Sample and Hold

During a conversion, the 'busy' signal from the AD574A ADC causes the AD583 Sample and Hold to hold its present value when the 'busy' signal is high, and starts sampling again when it is low.

#### 'A/D Busy' and Interrupt States

At the end of a conversion, the AD574 ADC's 'busy' signal goes low, and the AI status register shows that the analog input device is in the not-busy and interrupting state.

#### 'A/D Interrupt'

The actual 'A/D interrupt' signal (A/D INT) is a result of the logical ANDing of the INT STATE status bit in the AI status register, and the EOCINT ENABLE bit from the AI control register. The inverted result generates  $\overline{A/D}$  INT (an active low signal), which goes to the interrupt circuitry.

#### 'A/D Convert Out'

The 'A/D convert out' (A/D CO) signal is brought out to the distribution panel connector on the Data Acquisition Adapter.

The 'A/D convert out' signal is set (TTL high) when a conversion has been commanded by programming the convert start bit. The signal remains high until the conversion is complete. If the analog signals received by the on-board analog input device are from an external device that can be made to send data on receipt of a TTL high pulse, you may use a synchronization scheme in which the program's request for an analog-to-digital conversion triggers (using 'A/D convert out') the output of analog data from the external device.

#### 'A/D Convert Enable'

The 'A/D convert enable' (A/D CE) signal is brought out to the distribution panel connector on the Data Acquisition Adapter.

By holding the 'convert enable in' signal low (TTL), an external device can inhibit or delay all analog-to-digital conversions ordered by programming.

To be considered valid and allow an analog-to-digital conversion, the 'convert enable in' signal must remain high until the 'convert out' signal goes low again.

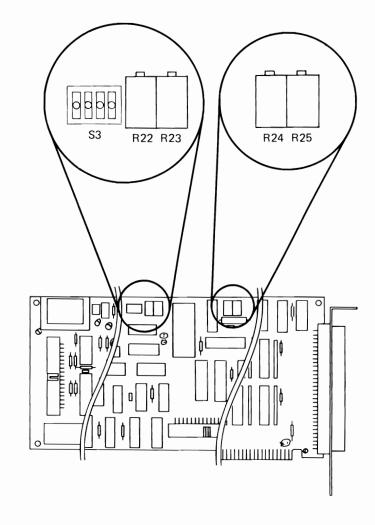

#### **Analog Input Potentiometers**

Four potentiometers (R22, R23, R24, and R25) on the Data Acquisition Adapter control bipolar offset, unipolar offset, gain, and common mode rejection for the analog input device. The following diagram shows the location of these potentiometers.

In the following "LSB" represents the weight of the least-significant bit of the 12-bit digital output code of the ADC.

The table shows the 1-LSB values for each analog input range.

| Range            | 1 LSB   |

|------------------|---------|

| 0 to +10 volts   | 2.44 mV |

| -5 to +5 volts   | 2.44 mV |

| -10 to +10 volts | 4.88 mV |

The ADC is intended to have a 1/2-LSB offset so the exact analog input for a given code will be in the middle of that code (halfway between the transitions to the codes above and below it). The information under "Bipolar Offset" and "Unipolar Offset" explains this 1/2-LSB offset.

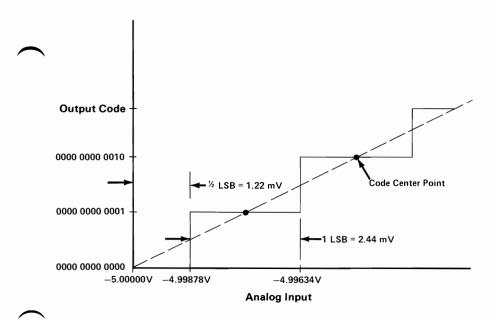

#### Bipolar Offset:

The value of R22 is set so the transition from the digital output code 0000 0000 0000 to 0000 0000 0001 occurs for an input voltage 1/2 LSB above negative full scale. R22 takes effect when a bipolar range (-5 to +5 volts or -10 to +10 volts) is selected.

The following shows the input voltages for the transition from the output code 0000 0000 0000 to 0000 0000 0001.

| Range            | Input Voltage for First Code<br>Transition |

|------------------|--------------------------------------------|

| -5 to +5 volts   | -4.99878 volts                             |

| -10 to +10 volts | -9.99756 volts                             |

The following shows the first few output-code transitions for the -5 to +5 volt range.

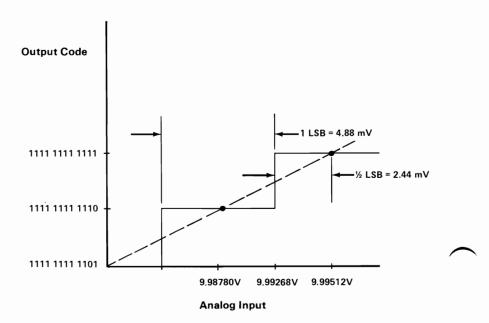

Gain:

The value of R23 is set so the last transition (1111 1111 1110 to 1111 1111 1111) occurs for an input voltage 1-1/2 LSB below full scale.

The following shows the input voltage for the transition from the output code 1111 1111 1110 to 1111 1111 1111.

| Range            | Input Voltage for Last Code<br>Transition |

|------------------|-------------------------------------------|

| 0 to +10 volts   | +9.99634 volts                            |

| -5 to +5 volts   | +4.99634 volts                            |

| -10 to +10 volts | +9.99268 volts                            |

The following shows the last few output-code transitions for the -10 to +10 volt range.

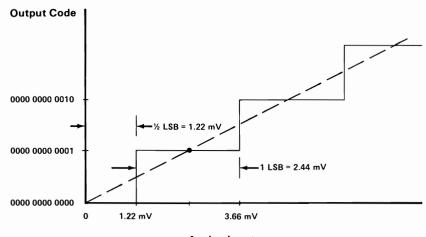

Unipolar Offset:

The value of R24 is set so the first transition (0000 0000 0000 to 0000 0000 0001) occurs for an input voltage of +1/2 LSB. R24 takes effect when the unipolar range (0 to +10 volts) is selected.

The following shows the first few output-code transitions for the 0 to +10 volt range.

Analog Input

Common Mode Rejection:

R25 allows for the reduction and balancing of the error caused by common mode noise (voltage common to both sides of an analog input channel). The common-mode input range specification for the analog input device is  $\pm 11$  volts maximum. The value of R25 is set so on the most sensitive range (-5 to +5 volts), the effect of common mode voltage is balanced on each side of zero volts. For example, a common mode voltage of +11 volts produces the same output code as a common mode voltage of -11 volts.

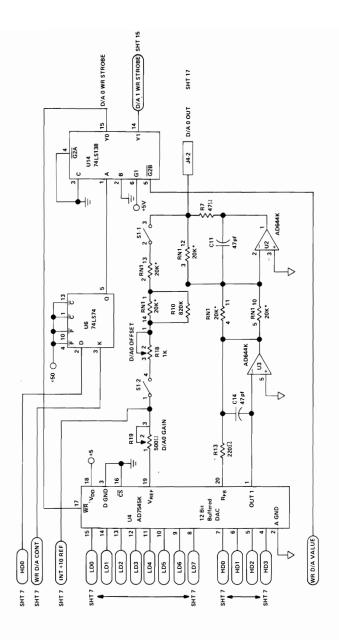

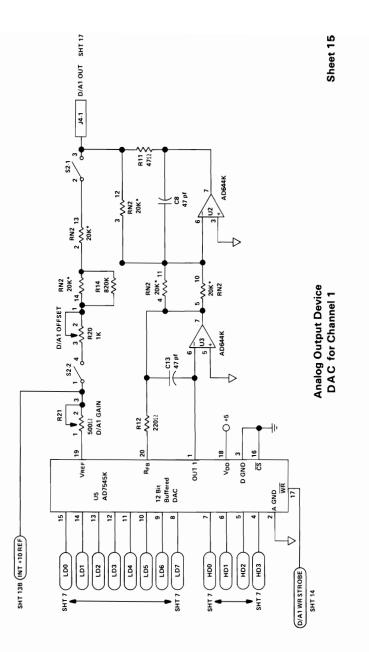

# Analog Output Subsystem

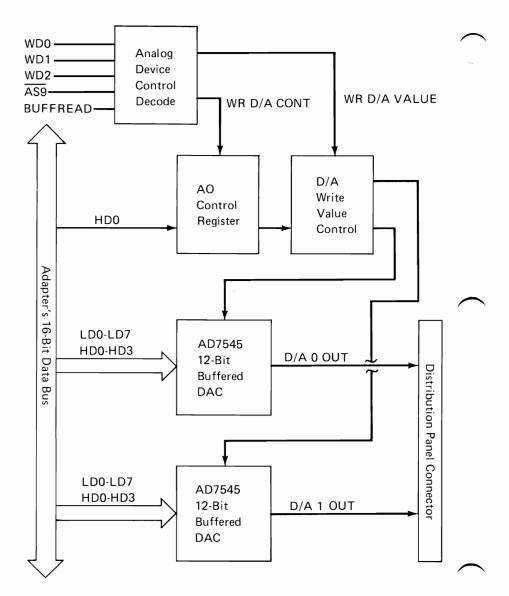

Following is a block diagram of the analog output subsystem.

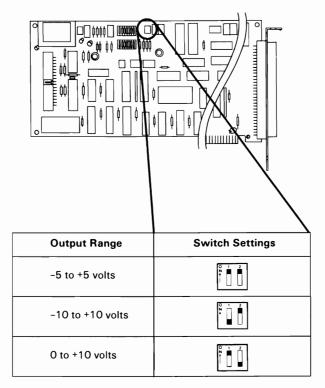

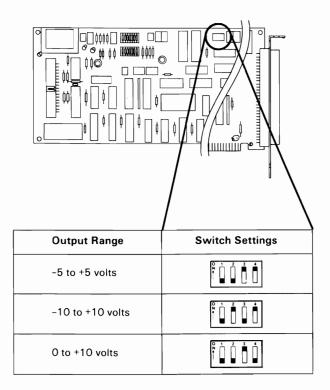

The Data Acquisition Adapter includes an on-board digital-to-analog output device with the following features:

- Two analog output channels, with each channel using separate DACs with 12-bit resolution

- Switch-selectable ranges for each converter

Each DAC converts digital values in the range of 0 to 4095 to voltages in one of three ranges. The switches on the adapter control voltage polarity and range.

The three switch-selectable ranges are:

- -5 to +5 volts

- -10 to +10 volts

- 0 to +10 volts

The settings of these switches determine the relationship between analog output values and the voltages from the analog output device. The relationship of the digital value to the analog output voltage depends on the range for which the hardware is configured. Because each analog output channel has its own DAC, the analog output range can be set for each channel. For example, in the 0 to +10 volt configuration, a digital value of 0 generates an output of 0 volts; a digital value of 2048 generates an output of +5 volts; and a digital value of 4095 generates an output of +9.997 volts.

### **Analog Output Device Control**

The control decode circuitry of the analog device decodes WD0 through WD2,  $\overline{\text{AS9}}$ , and BUFFREAD to generate the following control signals:

| WR D/A CONT  | Write digital-to-analog control:         |  |  |

|--------------|------------------------------------------|--|--|

|              | Controls the writing of the              |  |  |

|              | channel-select bit to the AO control     |  |  |

|              | register. The channel-select bit is used |  |  |

|              | to determine which digital-to-analog     |  |  |

|              | write strobe to generate.                |  |  |

| WR D/A VALUE | Write digital-to-analog value:           |  |  |

|              | Controls the generation of the           |  |  |

|              | digital-to-analog write strobes.         |  |  |

|              | WR D/A VALUE occurs when the             |  |  |

|              | AO data register is addressed.           |  |  |

### **Analog Output Device Registers**

| AO Control Register | When the 'write D/A value' signal occurs, the digital-to-analog write value control circuitry either strobes D/A 0 or D/A 1, on the basis of the channel-select bit in the AO control register.                                                                                                                                                                                                  |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AO Data Register    | When either AD7545 DAC receives a digital-to-analog write strobe, it latches a 12-bit digital value from the adapter's 16-bit data bus. Each DAC has data latches that are loaded when the AO data register address is written to. The AD7545 DAC then performs the digital-to-analog conversion, and an analog value is sent to the distribution panel connector by 'D/A 0 out' or 'D/A 1 out.' |

### **Analog Output Potentiometers**

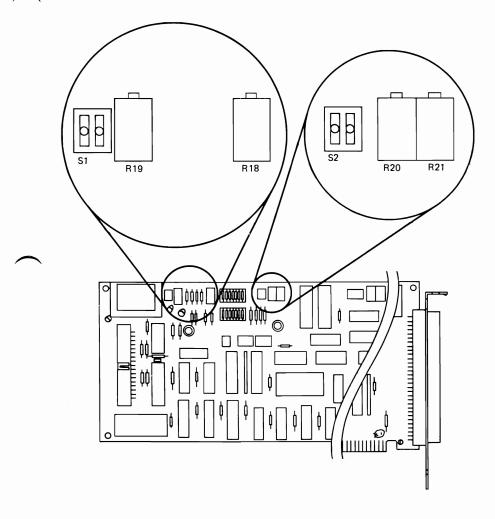

Four potentiometers (R18, R19, R20, and R21) on the Data Acquisition Adapter control bipolar offset and gain for the analog output device. The following diagram shows the location of these potentiometers.

Bipolar Offset:

R18 controls bipolar offset for channel 0, and R20 controls it for channel 1. The value of the potentiometer is set so a negative full-scale voltage is provided on the analog output channel when the digital code 0000 0000 0000 is sent to the DAC for that channel. The potentiometer takes effect when a bipolar range is selected. When the unipolar range is selected, the DAC output is 0 volts.

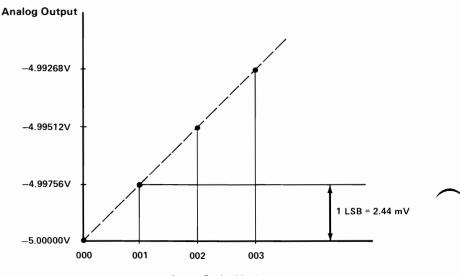

The following table lists the output voltages for the digital code 0000 0000 0000 (000 hex).

| Range            | Output Voltage for 000 Hex<br>Code |

|------------------|------------------------------------|

| 0 to +10 volts   | 0.00000 volts                      |

| -5 to +5 volts   | -5.00000 volts                     |

| -10 to +10 volts | -10.00000 volts                    |

The following shows the first few analog output voltages for the -5 to +5 volt range.

Input Code (Hex)

Gain:

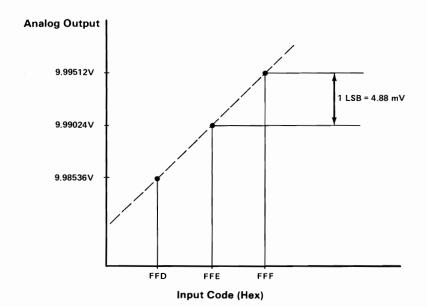

R19 controls gain for channel 0, and R21 controls it for channel 1. The value of the potentiomenter is set so a positive full-scale -1 LSB voltage is provided on the analog output channel when the digital code 1111 1111 1111 is sent to the DAC for that channel.

The following table lists the output voltages for the digital code 1111 1111 1111 (FFF hex).

| Range            | Output Voltage for FFF Hex<br>Code |

|------------------|------------------------------------|

| 0 to +10 volts   | +9.99756 volts                     |

| -5 to +5 volts   | +4.99756 volts                     |

| -10 to +10 volts | +9.99512 volts                     |

The following shows the last few analog output voltages for the -10 to +10 volt range.

August 15,1984 © Copyright IBM Corporation 1984

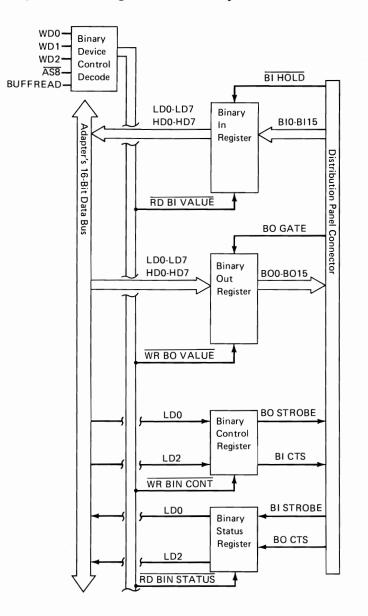

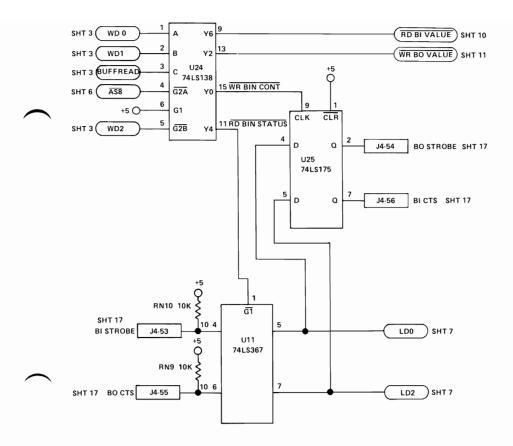

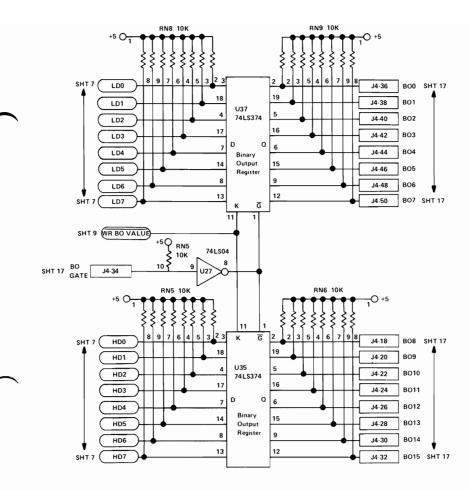

# **Binary I/O Device**

Following is a block diagram of the binary I/O device.

The Data Acquisition Adapter's binary I/O device has the following features:

- A 16-bit binary output port (BO0 through BO15)

- A 16-bit binary input port (BI0 through BI15)

- Input and output handshaking over the 'strobe' and 'clear-to-send' lines

- Direct control using BO GATE ('binary out gate') and BI HOLD ('binary in hold').

Digital signals have only two voltage states: On (high, +3 volts) and Off (low, +0.2 volts). Digital signals in this range are called *TTL signals*, because they are the proper levels to be interpreted by the transistor-to-transistor logic circuitry. These signals have many uses in data acquisition and control applications. Among these are sensing the state of two-state devices and controlling devices that require two-state control signals.

# **Binary I/O Device Control**

The use of the  $\overline{AS8}$  strobe causes the binary I/O device to be accessed as device number 8.

The  $\overline{AS8}$  strobe as an enable, the WD0 through WD2 word bits, and the BUFFREAD signal are used to decode which binary decode operation is to occur.

Following are the four decode operations:

| WR BIN CONT   | Write binary control: Controls the<br>latching of the binary output strobe<br>(BO STROBE) and the binary input<br>clear-to-send (BI CTS) bits by the binary<br>control register. |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RD BIN STATUS | Read binary status: Controls the reading<br>of the binary input strobe (BI STROBE)<br>and the binary output clear to send<br>(BO CTS) bits by the binary status<br>register.     |

| WR BO VALUE   | Write binary value: Controls the writing<br>of the binary output word (BO0 through<br>BO15) to the binary output register.                                                       |

| RD BI VALUE   | Read binary value: Controls the reading<br>of the binary input word (BI0 through<br>BI15) from the binary input data register.                                                   |

# **Binary I/O Device Registers**

Following is a description of the binary I/O device registers.

| <br><b>Binary Control Register</b> | Contains the BO STROBE bit and<br>the BI CTS bit. These bits do not<br>physically cause or prevent binary<br>I/O events from occurring. They are<br>programming control bits.                                                                                                                                                                                                                                                                                                                                                       |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Binary Status Register             | Allows the status of BO CTS and<br>BI STROBE bits to be monitored.<br>These bits do not physically cause or<br>prevent binary I/O events from<br>occurring. They are programming<br>status bits.                                                                                                                                                                                                                                                                                                                                    |

| Binary Input Register              | When <b>BI HOLD</b> is brought high (or if<br>no connection is made), the binary<br>input register is not latched and<br>allows the current state of the binary<br>input lines to be monitored by reading<br>the binary input register.<br>Grounding <b>BI HOLD</b> causes the<br>binary input register to latch the<br>current state of all binary input lines.<br>If the grounding of the <b>BI HOLD</b> line<br>is maintained, any later read will<br>obtain the value that was present<br>when the line was initially grounded. |

| <br><b>Binary Output Register</b>  | Contains the binary output word<br>(BO0 through BO15). Grounding the<br>BO GATE signal places the binary<br>output port in the tri-state condition<br>(all points floating). The binary<br>outputs are gated out when the<br>BO GATE signal is brought high<br>(or if no connection is made).                                                                                                                                                                                                                                       |

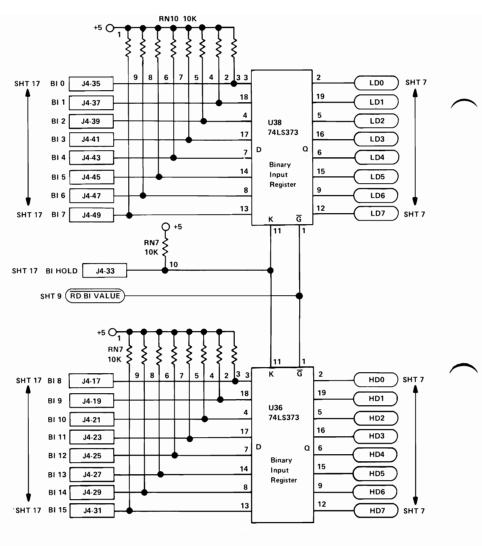

The Data Acquisition Adapter's binary I/O device consists of two subsystems that use low-power Schottky logic:

- Binary input

- Binary output

# **Binary Input Subsystem**

Following is a description of the binary input subsystem.

# Binary Input Port (BI0 through BI15)

All bits of the binary input port (BI0 through BI15) are pulled to their high state internally. This means that if nothing is connected to the binary input port, execution of a binary input function returns a value of 65535 (all bits set to 1).

The input port of the Data Acquisition Adapter's binary I/O device can be used to sense the state of up to 16 individual binary signals.

The binary input port also can be used for input of binary data words (16-bit) from another device.

## **Binary Input Hold**

The entire binary input port may be latched at any time by pulling the  $\overline{BI HOLD}$  signal low. These and all other data and communication lines are pulled high through internal resistors to +5 volts. No connections to them are necessary unless their features are to be used.

## **Binary Input Handshaking**

Binary input samples can be synchronized with binary words generated by an external device. The external device must be able to send parallel binary data when it receives a signal from the Data Acquisition Adapter's binary I/O device. It also must be able to generate a TTL signal that indicates the data word is valid and should be sent by the Data Acquisition Adapter.

## **Binary Output Subsystem**

Following is a description of the binary output subsystem.

## Binary Output Port (BO0 through BO15)

This subsystem uses high-power, tri-state, bus-driving devices. Changes in the binary output word are carried out on a per-bit basis. Only those bits affected by a change in the output word are actually changed. All others remain the same.

The output port of the binary I/O device supplies 16 high/low signals under program control. As with the input port, these signals can be used individually or considered as a 16-bit data word.

#### **Binary Out Gate**

You may place the output port in tri-state by pulling the binary out gate (BO GATE) lines low. These and all other data, handshaking, and control lines are pulled high by internal resistors to +5 volts. No connections to them are necessary unless your application requires handshaking or control.

#### **Binary Output Handshaking**

Because all communication lines are internally pulled up to their logical true state, you can use or not use binary output handshaking, depending on the requirements of your communication setup.

Binary output can be synchronized with the data input capabilities of the external device. The external device must be able to send a TTL signal to indicate it is ready for new data. It also must be able to accept parallel binary data when it recieves a signal from the Data Acquisition Adapter's binary I/O device indicating the data is available.

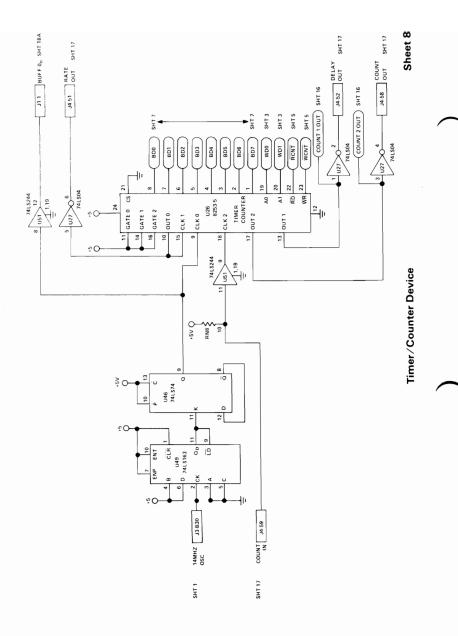

# **Timer/Counter Device**

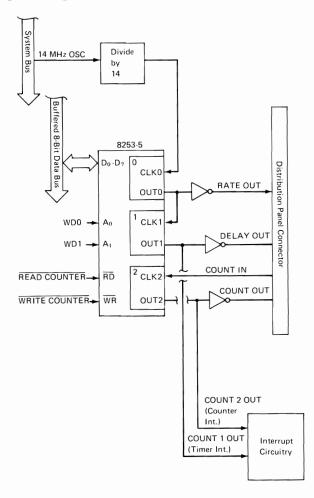

The timer/counter device is an 8253-5 Programmable Interval Timer. The timer/counter device provides three independent, down-counting, 16-bit counters. Each counter can be programmed to operate in one of four modes. In this implementation, Counters 0 and 1 are cascaded to provide a 32-bit timer. Counter 2 is not cascaded and provides an independent 16-bit timer/counter. These counters can be used to generate interrupts, provide pulses (or pulse trains) to the distribution panel connector (RATE OUT, DELAY OUT, and COUNT OUT), and count events (COUNT IN).

Following is a diagram of the timer/counter device.

# **Timer/Counter System Interface**

Following is a description of how the Data Acquisition Adapter controls its timer/counter device.

| <b>BD0 - BD7</b> | The Data Acquisition Adapter's buffered<br>data bus lines are connected to data lines<br>(D0 through D7) of the timer/counter<br>device's internal data-bus buffer. |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RD CNT           | Read counter: Connected to the RD pin<br>of the timer/counter device. Used as a<br>control signal when reading the values of<br>the counters.                       |

| WR CNT           | Write counter: Connected to the WR pin<br>of the timer/counter device. Used as a<br>control signal when writing mode<br>information and loading the counters.       |

| WD0 and WD1      | Connected to the A0 and A1 pins of the timer/counter device. They select which of the three counters to be operated on, and address the control register.           |

The following lists the resulting timer/counter device operations performed based on the values of the timer/counter device's address and control signals.

Note: The CS pin of the timer/counter device is tied low.

| ĊŚ | RD | WR | <b>A</b> <sub>1</sub> | <b>A</b> <sub>0</sub> | Description          |

|----|----|----|-----------------------|-----------------------|----------------------|

| 0  | 1  | 0  | 0                     | 0                     | Load Counter 0       |

| 0  | 1  | 0  | 0                     | 1                     | Load Counter 1       |

| 0  | 1  | 0  | 1                     | 0                     | Load Counter 2       |

| 0  | 1  | 0  | 1                     | 1                     | Write Mode Word      |

| 0  | 0  | 1  | 0                     | 0                     | Read Counter 0       |

| 0  | 0  | 1  | 0                     | 1                     | Read Counter 1       |

| 0  | 0  | 1  | 1                     | 0                     | Read Counter 2       |

| 0  | 0  | 1  | 1                     | 1                     | No-Operation 3-State |

| 1  | X  | Х  | х                     | Х                     | Disable 3-State      |

| 0  | 1  | 1  | X                     | Х                     | No-Operation 3-State |

# 32-Bit Timer

Following is a description of the output of the 32-bit timer (Counters 0 and 1), and how it is clocked.

#### First Stage (Counter 0)

| CLK 0                    | A 1.023-MHz signal (50% duty cycle) from the system bus' 14-MHz OSC and divide-by-14 circuitry.     |  |

|--------------------------|-----------------------------------------------------------------------------------------------------|--|

| OUT 0                    | Output of Counter 0.                                                                                |  |

| RATE OUT                 | Inverted state of OUT 0 that is brought to the distribution panel connector.                        |  |

| Second Stage (Counter 1) |                                                                                                     |  |

| CLK 1                    | The Counter-1 clock. The output of<br>Counter 0 (OUT 0) is cascaded into the<br>counter of clock 1. |  |

| OUT 1                    | Output of Counter 1. Provides the 'count 1 out' signal that is used by the interrupt circuitry.     |  |

| DELAY OUT                | Inverted state of OUT 1 that is brought to the distribution panel connector.                        |  |

# **16-Bit Timer/Counter**

Following is a description of the output of the 16-bit timer/counter (Counter 2), and how it is clocked.

| CLK 2     | The Counter-2 clock.                                                                    |

|-----------|-----------------------------------------------------------------------------------------|

| COUNT IN  | Clocks Counter 2.                                                                       |

| OUT 2     | Output of Counter 2. Provides the 'count 2 out' signal used by the interrupt circuitry. |

| COUNT OUT | Inverted state of OUT 2 that is brought to the distribution panel connector.            |

# **Counter Modes**

The following counter modes apply to Counters 0 through 2.

**Note:** "Output" in the following timing diagrams refers to the OUT 0, OUT 1, and OUT 2 pins of the timer/counter device. Counter outputs, RATE OUT, DELAY OUT, and COUNT OUT, on the distribution panel connector are the inverted state of OUT 0, OUT 1, and OUT 2.

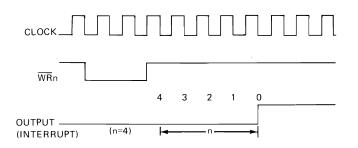

#### Mode 0: Interrupt on Terminal Count

Initially, the output is low after the mode-set operation. After the count is loaded into the selected count register, the output remains low, and the counter counts. When terminal count is reached, the output goes high and remains high until the selected count register is reloaded with the mode or a new count is loaded. The counter continues to decrease after terminal count is reached.

Rewriting a counter register during counting results in the following:

- A Write to the first byte stops the current counting.

- A Write to the second byte starts the new count.

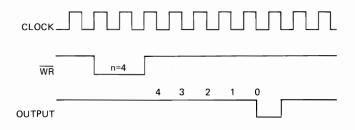

Following is the timing diagram for mode 0.

#### Mode 0: Interrupt on Terminal Count

### Mode 1: Programmable One-Shot

This mode is not used because the timer/counter device's gate pins (GATE 0 through GATE 2) are tied high.

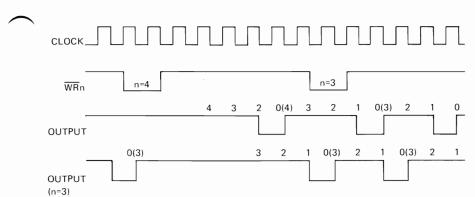

#### Mode 2: Rate Generator

Divide-by-N counter. The output is low for one period of the input clock. The period from one output pulse to the next equals the number of input counts in the count register. If the count register is reloaded between output pulses, the present period is not affected, but the next period reflects the new value.

When the mode is set, the output remains high until the count register is loaded. The output can then also be synchronized by programming.

Following is the timing diagram for mode 2.

#### Mode 2: Rate Generator

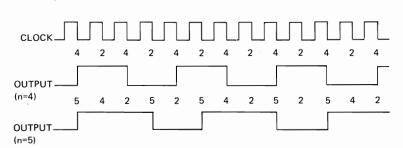

#### Mode 3: Square-Wave Rate Generator

This mode is similar to mode 2, except the output remains high until half the count is complete (for even numbers), then goes low for the other half. This is accomplished by decrementing the counter by 2 on the falling edge of each clock pulse. When the counter reaches terminal count, the state of the output changes, and the counter is reloaded with the full count; the complete process then repeats.

If the count is odd and the output high, the first clock pulse after the count is loaded, decreases the count by 1. Subsequent clock pulses decrease the clock by 2. After time-out, the output goes low and the full count is reloaded. The first clock pulse after the reload, decreases the counter by 3. Subsequent clock pulses decrease the count by 2 until time-out. Then the complete process repeats. In this way, if the count is odd, the output will be high for (N + 1)/2 counts and low for (N - 1)/2 counts.

Following is the timing diagram for mode 3.

#### Mode 3: Square Wave Generator

#### 52 Data Acquisition Adapter

#### Mode 4: Software-Triggered Strobe

After the mode is set, the output is high. When the count is loaded, the counter begins counting. When the counter reaches terminal count, the output goes low for one input clock period, then goes high again.

If the count register is reloaded during counting, the new count is loaded on the next CLK pulse.

Following is the timing diagram for mode 4.

#### Mode 4: Software Triggered Strobe

#### Mode 5: Hardware-Triggered Strobe

This mode is not used because the pins for gates 0 through 2 are tied high.

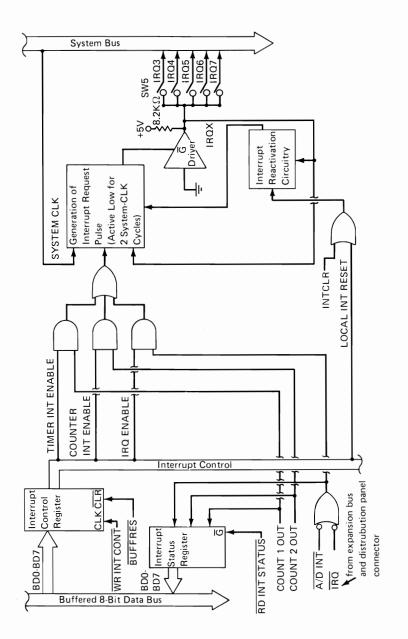

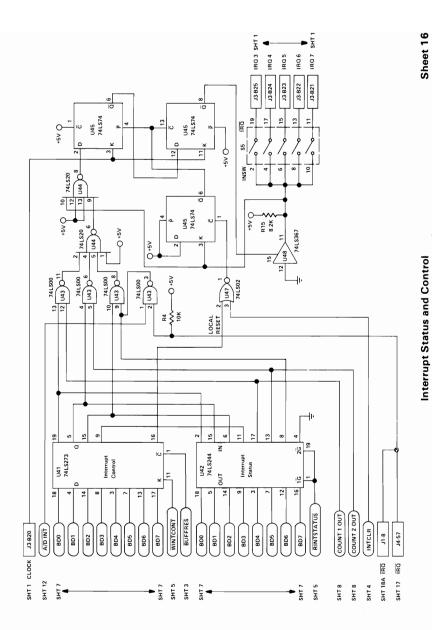

# **Interrupt Circuitry**

The following is a block diagram of the interrupt circuitry.

The Data Acquisition Adapter can generate an interrupt from the following individually maskable sources:

- 32-bit timer (cascaded 16-bit Counters 0 and 1 of the timer/counter device)

- 16-bit externally-clocked timer/counter (Counter 2 of the timer/counter device)

- ADC 'end of conversion' signal

- IRQ external interrupt (on the distribution panel connector and the expansion bus).

Interrupts generated by the Data Acquisition Adapter can be set to an interrupt level in the range of IRQ3 through IRQ7. The interrupt level is set with the switches of S5 on the adapter and must be set before adapter installation. IRQ7 is recommended.

# **Interrupt Control Register**

Following is a description of the bits of the interrupt control register.

| Bit 0     | TINT ENABLE: Enables 32-bit timer interrupts (Counters 0 and 1).                                                                                |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 1     | CINT ENABLE: Enables 16-bit timer/counter interrupts (Counter 2).                                                                               |

| Bit 2     | IRQ ENABLE: Enables the $\overline{IRQ}$ (external interrupt) line and analog-to-digital end-of-conversion interrupts as sources of interrupts. |

| Bit 3     | Reserved for reading status.                                                                                                                    |

| Bit 4 - 6 | Not used.                                                                                                                                       |

| Bit 7     | LINT RESET: Performs the local-reset function.                                                                                                  |

**Note:** Power-on-reset (**BUFFRES**) resets the interrupt control register (clearing all bits and disabling interrupts).

# **Interrupt Status Register**

Following is a description of the bits of the interrupt status register.

| Bits 0 – 3 | Provided for reading the status of the<br>corresponding interrupt-enable bits listed under<br>"Interrupt Control Register". Bit 3 is not<br>currently used.                      |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 4      | TINT STAT: The timer interrupt status (COUNT 1 OUT), which is the state of the output of the second chained timer stage (Counter 1 of the timer/counter device).                 |

| Bit 5      | CINT STAT: The counter interrupt status (COUNT 2 OUT), which is the state of the output of the 16-bit timer/counter (Counter 2).                                                 |

| Bit 6      | IRQ STAT: The $\overline{IRQ}$ (external-interrupt) status.<br>The on-board 'A/D interrupt' signal is logically<br>ORed into the $\overline{IRQ}$ (external-interrupt) function. |

| Bit 7      | Read back as a 0.                                                                                                                                                                |

## **Interrupt Request Pulse**

The corresponding three interrupt-enable and three interrupt-status lines are logically ANDed. Any combination of the three interrupt sources may be enabled. The enabled interrupts are logically ORed to generate the adapter-interrupt trigger signal. This signal causes the generation of an 'interrupt request out' pulse by enabling a tri-state driver to be active low for two cycles of the system clock. The output of this driver is connected to the desired system interrupt level (IRQ3 through IRQ7) by switch S5. When not active low, the tri-state driver is floating and allows other adapters to share the interrupt line.

## **Interrupt Reactivation**

When the shared-interrupt line pulses low, regardless of whether the Data Acquisition Adapter or another interrupt-sharing adapter was the source, the interrupt-reactivation circuitry prevents the Data Acquisition Adapter from generating interrupts. Thus, a single interrupt causes deactivation of additional interrupts. Additional interrupts are reactivated by either the 'local reset' signal (only one Data Acquisition Adapter reactivated) or the INTCLR signal (all interrupt-sharing adapters reactivated). A logical OR of the 'local reset' or INTCLR shared-interrupt reactivation signals starts the interrupt-reactivation circuitry. Following is a description of the two shared-interrupt reactivation signals.

### Local Interrupt Reset

The local-interrupt-reset bit in the interrupt control register controls the reactivation of only one Data Acquisition Adapter. The particular adapter is singled out by the adapter-number bits (A10 and A11) in the adapter's I/O address space.

#### **Global Interrupt Reset**

A global-interrupt reset also can be performed. This resets the interrupt circuitry of all adapters sharing a particular interrupt level. The only requirement is that the adapters support interrupt sharing. The Data Acquisition Adapter does support interrupt sharing.

To perform a shared-interrupt global reset, an I/O Write to an address hex 02Fx (02F3 through 02F7) is performed for a particular interrupt level (IRQ3 through IRQ7). Thus, to reset all adapters sharing interrupt IRQ7, an I/O Write to hex 02F7 is performed. The output value is not important.

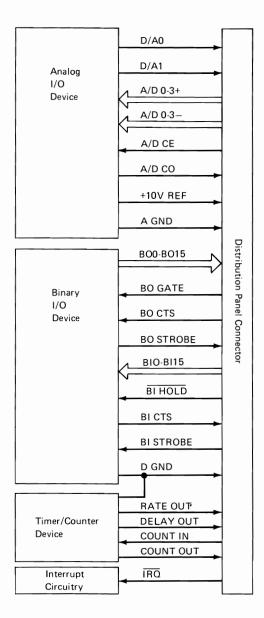

# **Distribution Panel Connector**

Following is a block diagram of the signals of the distribution panel connector, J4.

# **Distribution Panel Connector Signals**

The following is a description of how the distribution panel connector, J4, provides access to the interrupt circuitry, and the analog I/O, binary I/O, and timer/counter devices.

| D/A 0, D/A 1     | DAC outputs.                                                                                                                                   |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| EXT +10 V REF    | 10-volt reference output.                                                                                                                      |

| A GND            | Analog ground: The system ground reference for the analog devices in the system.                                                               |

| A/D 0- to A/D 3- | Channels 0 through 3 ADC inputs (low).                                                                                                         |

| A/D 0+ to A/D 3+ | Channels 0 through 3 ADC inputs (high).                                                                                                        |

| D GND            | Digital ground: The system ground reference for the digital devices in the system.                                                             |

| A/D CE           | 'Convert enable' input for the ADC.<br>When high, enables conversion.                                                                          |

| A/D CO           | 'Convert out' indicator for the ADC.<br>When high, indicates a conversion was<br>requested. Returns to low when the<br>conversion is complete. |

| <b>BI HOLD</b>   | Binary-input hold: Latch control for the binary input port. When low, the binary input device latches the state of all input lines.             |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| BI STROBE        | (Input) Binary input strobe: When high, indicates the binary input data is available.                                                           |

| BI0 - BI15       | Binary input port, bits 0 through 15.                                                                                                           |

| BO0 - BO15       | Binary output port, bits 0 through 15.                                                                                                          |

| BO GATE          | (Input) Binary output gate: Tri-state<br>enable for the binary output port. When<br>low, the binary outputs (BO0 through<br>BO15) are floating. |

| <b>BO STROBE</b> | (Output) Binary output strobe: When high, indicates that new data was sent.                                                                     |

| BO CTS           | (Input) Binary output clear-to-send:<br>When high, permits new binary-output<br>port data to be sent.                                           |

| BI CTS           | (Output) Binary input clear-to-send:<br>When high, indicates the binary input<br>data is being requested.                                       |

|          | ĪRQ       | (Input) External-device,<br>interrupt-request: Active low.                                                                              |

|----------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| <b>`</b> | RATE OUT  | Output from the first stage of the 32-bit timer (Counter 0). The 'rate out' signal is the inverse of the timer/counter device output.   |

|          | DELAY OUT | Output from the second stage of the 32-bit timer (Counter 1). The 'delay out' signal is the inverse of the timer/counter device output. |

|          | COUNT OUT | Output from the 16-bit counter device<br>(Counter 2). The 'count out' signal is the<br>inverse of the timer/counter device<br>output.   |

|          | COUNT IN  | Input to the 16-bit counter device (Counter 2).                                                                                         |

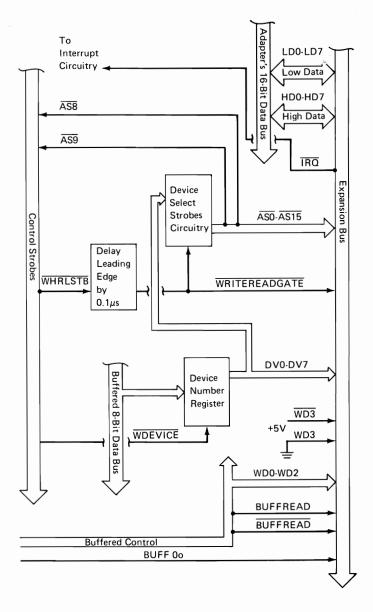

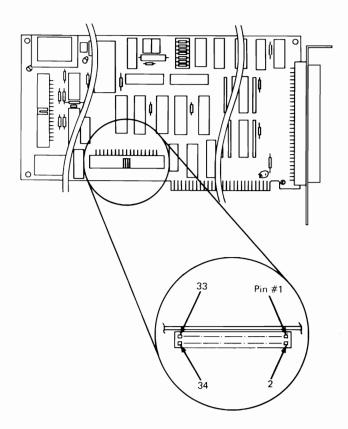

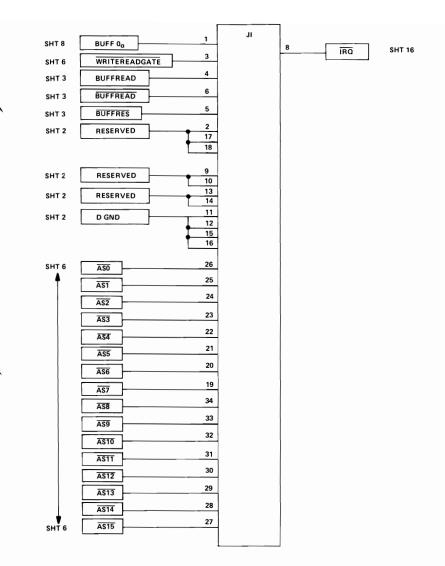

# **Expansion Bus**

Following is a block diagram showing device selection signals, control signals, and data bus lines which make up the expansion bus.

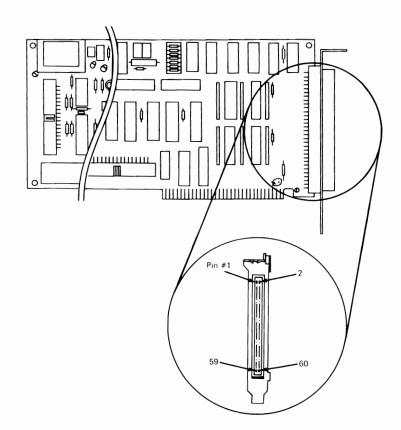

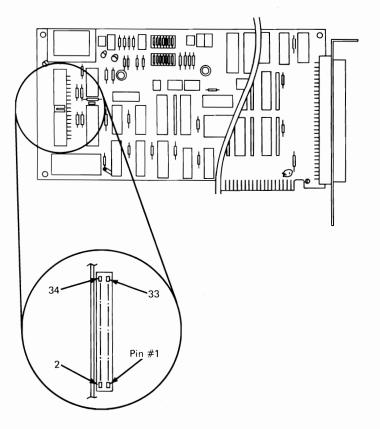

The expansion bus is an expansion interface for data acquisition and control adapters. The bus consists of two 34-pin transition connectors, J1 and J2, on the Data Acquisition Adapter.

All drivers on the bus are intended to be low-power Schottky

(LS) TTL bus drivers or equivalent devices. Such devices can drive below 0.4 volts at 12 milliamperes load current, and above 2.4 volts at 2.6 milliamperes.

All receivers on the bus are intended to be no more than two LS TTL loads for each external device on any bus line. Such devices will present a load current of no more than 0.8 milliamperes sourcing at 0.4 volts, and no more than 40 microamperes sinking at 2.4 volts. A single LS TTL load for each external device on any bus line is preferred.

Drivers on the bidirectional data lines must be tri-state devices enabled only during the appropriate strobes.

# **Expansion Bus Signals**

Following is a description of the signals on the expansion bus.

| BUFF 0 <sub>0</sub>                   | (Output) OSC signal divided by 14 (1.023 MHz).                                                                                                                     |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WRITEREADGATE                         | (Output) Active low strobe for all<br>devices. AS16 through AS255<br>strobes can be created by decoding<br>DV0 through DV7 and using the<br>signal, WRITEREADGATE. |

| BUFFREAD                              | (Output) When high, indicates a read is occurring. When low, indicates a write is occurring.                                                                       |

| BUFFREAD                              | (Output) Inverse of BUFFREAD.                                                                                                                                      |

| BUFFRES                               | (Output) inverse of RESET DRV.<br>Performs system reset and<br>initialization.                                                                                     |

| ĪRQ                                   | (Input) External, interrupt request.<br>Active low.                                                                                                                |

| $\overline{AS0}$ to $\overline{AS15}$ | (Outputs) Active low strobes for devices 0 through 15. Must be low for 0.4 microseconds.                                                                           |

|   | WD3       | Word number bit 3, fixed high.                                                                                    |

|---|-----------|-------------------------------------------------------------------------------------------------------------------|

|   | WD3       | Word number bit 3, grounded.                                                                                      |

| - | HA4 - HA7 | Reserved expansion signals; grounded.                                                                             |

|   | DV0 - DV7 | (Output) Device-number bits. Select one of 256 possible devices.                                                  |

|   | LD0 - LD7 | (Inputs/Outputs) Low byte of the adapter's 16-bit data bus.                                                       |

|   | HD0 - HD7 | (Inputs/Outputs) High byte of the adapter's 16-bit data bus.                                                      |

|   | WD0 - WD2 | Word number bits 0 through 2 (system-bus address lines A12 through A14 are buffered and renamed WD0 through WD2). |

Following is a diagram of the expansion bus read timing.

Following is a diagram of the expansion bus write timing.

68 Data Acquisition Adapter

August 15, 1984 © Copyright IBM Corporation 1984

# **Programming Considerations**

This section describes the programming considerations for the Data Acquisition Adapter.

## **Address Decoding**

The following table shows address decoding.

| A15 A14 A13 A12 | A11 A10     | A | 9 A 8 | A A | 7 А6 | 6 A5 | A4 | A3 | A2 / | A1 | A0          |

|-----------------|-------------|---|-------|-----|------|------|----|----|------|----|-------------|

| Register Select | Card Select | 1 | 0     | 1   | 1    | 1    | 0  | 0  | 0    | 1  | Byte Select |

- Register Select selects one of 16 word registers (0 through 15). Only registers 0 through 13 are used.

- Card Select selects the adapter number (0 through 3).

- A1 through A9 are a fixed pattern to select Data Acquisition Adapters.

- A0 selects the high or low byte of a 16-bit word register.

The base addresses of the Data Acquisition adapters are:

| Adapter Number | Base Address (Hex) |

|----------------|--------------------|

| 0              | 02E2               |

| 1              | 06E2               |

| 2              | 0AE2               |

| 3              | OEE2               |

## Registers

Each Data Acquisition Adapter has 16 (two-byte) word registers through which all access to the Data Acquisition Adapter is made. The registers allow access to the Data Acquisition Adapter's on-board and expansion data-acquisition and control devices, the adapter's interrupt registers and device number register, and the timer/counter device registers.

The following table shows the Data Acquisition Adapter's registers.

| Register    | Name                        | Function                     |

|-------------|-----------------------------|------------------------------|

| 0           | Device Register 0           | Write values to, and read    |

| 1           | Device Register 1           | values from, the on-board    |

| 2           | Device Register 2           | and external devices         |

| 3           | Device Register 3           |                              |

| 4           | Device Register 4           |                              |

| 5<br>6<br>7 | Device Register 5           |                              |

| 6           | Device Register 6           |                              |

| 7           | Device Register 7           |                              |

|             |                             |                              |

| 8           | Timer/Counter 0             | Read/load Counter 0          |

|             | Register                    |                              |

| 9           | Timer/Counter 1             | Read/load Counter 1          |

| 10          | Register                    | Budd (land Country 2         |

| 10          | Timer/Counter 2<br>Register | Read/load Counter 2          |

| 11          | Timer/counter               | Controls the operation       |

|             | Control                     | of Counters 0 through 2.     |

|             | Register                    | -                            |

|             |                             |                              |

| 12          | Device Number               | Selects device               |

|             |                             |                              |

| 13          | Interrupt Registers         | Interrupt control and status |

| 14          |                             | Not used                     |

| 15          |                             | Not used                     |

## **Device Registers**

Eight register addresses have been reserved for reading and writing the registers on the on-board and external devices. The device is selected using the device-number register. These registers may then be used for access to the registers of that device. These registers are both read and write registers, and often two different functions will be decoded for the read and write.

#### **Analog Input Device Registers**

The on-board analog input (AI) device, accessed as device number 9, has four channels. External AI devices can be added to the expansion interface. These external AI devices have up to 256 channels, use ADCs with up to 16 bits of resolution, and are accessed with a different device number, but with the same register format as the on-board AI device.

| Register | Read/Write | Name       | Function                           |

|----------|------------|------------|------------------------------------|

| 0        | Write      | AI Control | Sets up and controls the register. |

| 0        | Read       | Al Status  | Returns status of the hardware.    |

| 2        | Read       | Al Data    | Returns current<br>analog value.   |

The AI device has the following registers.

## Following is a description of the bits of the AI control register.

| Bit  | Name          | Function                                                                                                                         |

|------|---------------|----------------------------------------------------------------------------------------------------------------------------------|

| 0    | Convert Start | Setting this bit starts an<br>analog-to-digital<br>conversion.                                                                   |

| 1    | Short Cycle   | Reserved for enabling a short cycle conversion.                                                                                  |

| 2    | EOCINT Enable | End-of-conversion<br>interrupt enable. When<br>set, an end-of-conversion<br>(conversion complete) will<br>generate an interrupt. |

| 3-7  |               | Not used                                                                                                                         |

| 8-15 | Channel       | Channels 0 through 255.<br>On-board Al device uses<br>only channels 0 through 3.                                                 |

### Following is a description of the bits of the AI status register.

| Bit    | Name          | Function                                                                                                                                                 |

|--------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | Busy State    | When set, indicates that<br>the ADC is in the process<br>of doing a conversion and<br>data is not yet valid.                                             |

| 1      | Int State     | When set, indicates that a conversion has ended (not busy and interrupting state). If the EOCINT enable bit is set (enabled), an interrupt is generated. |

| 2      | EOCINT Enable | Read back of state of<br>EOCINT enable bit in Al<br>control register.                                                                                    |

| 3 - 15 |               | Not used                                                                                                                                                 |

$\frown$

Following is a description of the bits of the AI data register.

| Bit  | Name | Function                                                                                                                                                                                                                            |

|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0-15 | Data | Contains the data value from<br>the last conversion. Valid<br>only if the busy bit in the AI<br>status register is cleared. Bits<br>0 through 11 will contain data<br>from the 12-bit ADC. Bits 12<br>through 15 will all be zeros. |

#### AI Device Access Strategy

The following outlines the access strategy for the AI device. Note that because channel selection takes a while, routines that repeatedly access a single channel would want to select the channel only once before data acquisition.

#### **Polling Method**

To use the polling method, do the following:

- 1. Set the device number in the device-number register to 9.

- 2. Set the channel and simultaneously disable conversion by setting the convert start bit to 0.

- 3. Wait for the channel multiplexer to settle (approximately 20 microseconds).

- 4. Request a conversion by setting the convert start bit to 1 and set the same channel.

- 5. Wait for the busy stat bit to equal 0.

- 6. Enable reading of the ADC's data by setting the convert start bit to 0, and set the same channel.

- 7. Read the data value.

#### **Interruption Method**

To use the interruption method, do the following:

- 1. Set the device number in the device-number register to 9.

- 2. Set the channel and simultaneously disable conversion by setting the convert start bit to 0.

- 3. Wait for the channel multiplexer to settle (approximately 20 microseconds).

- 4. Request a conversion by setting the convert start bit to 1, and set the same channel.

- 5. Set the EOCINT enable bit to 1 to enable an end-of-conversion interrupt.

- 6. After servicing the interrupt, set the EOCINT enable bit to 0 to disable AI interrupts.

## **Analog Output Device**

The analog output (AO) device has two channels, uses 12-bit DACs, and is accessed as device number 9.

External AO devices can be added to the expansion interface. These devices have up to 256 channels, use DACs with up to 16-bit resolution, and are accessed with a different device number, but use the same register format as the analog output device.

The AO device has the following registers.

| Register | Read/Write | Name       | Function                           |

|----------|------------|------------|------------------------------------|

| 1        | Write      | AO Control | Sets up and controls the register. |

| 3        | Write      | AO Data    | Output value.                      |

Following is a description of the bits of the AO control register.

| Bit  | Name    | Function                                                                       |

|------|---------|--------------------------------------------------------------------------------|

| 0-7  |         | Not used                                                                       |

| 8-15 | Channel | Selects channel 0 through<br>255. On-board AO device<br>uses channels 0 and 1. |

Following is a description of the bits of the AO data register.

| Bit  | Name | Function                                                                                                                                                        |

|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0-15 | Data | The value to be<br>provided to the<br>selected channel.<br>Sets bits 0 through 11<br>with data for the<br>12-bit DACs, and bits<br>12 through 15 with<br>zeros. |

#### **AO Device Access Strategy**

To use the AO device access strategy, do the following:

- 1. Set the device number to 9 in the device-number register.

- 2. Set the channel in the AO control register.

- 3. Write the data value to the AO data register.

August 15, 1984 © Copyright IBM Corporation 1984

## **Binary Input/Output Device**

This on-board device, which is accessed as device number 8, is a parallel binary (TTL) I/O device. It has one 16-bit output port, one 16-bit input port, and support for handshaking lines.

Binary I/O expansion devices can be attached to the expansion interface. These devices are accessed with a different device number, but use the same register format as the binary I/O device.

| Reg. | Read/Write | Name           | Function                                            |

|------|------------|----------------|-----------------------------------------------------|

| 0    | Read       | Binary Status  | The current state of the handshaking input lines.   |

| 0    | Write      | Binary Control | Controls the state of the handshaking output lines. |

| 2    | Read       | Binary Input   | Data register for binary input port.                |

| 2    | Write      | Binary Output  | Data register for binary output port.               |

The binary I/O device has the following registers.

### Following is a description of the bits of the binary status register.

| Bit  | Name      | Function                                                                                                  |

|------|-----------|-----------------------------------------------------------------------------------------------------------|

| 0    | BI Strobe | Indicates the state of the<br>binary input port's 'BI strobe'<br>input handshaking line.                  |

| 1    |           | Reserved                                                                                                  |

| 2    | BO CTS    | Indicates the state of the<br>binary output port's 'clear to<br>send' (BO CTS) input<br>handshaking line. |

| 3    |           | Reserved                                                                                                  |

| 4-15 |           | Not used                                                                                                  |

Following is a description of the bits of the binary control register.

| Bit  | Name      | Function                                                                                                    |

|------|-----------|-------------------------------------------------------------------------------------------------------------|

| 0    | BO Strobe | This bit sets and clears the<br>binary output port's 'BO<br>strobe' output handshaking<br>line.             |

| 1    |           | Reserved                                                                                                    |

| 2    | BICTS     | This bit sets and clears the<br>binary input port's 'clear to<br>send' (BI CTS) output<br>handshaking line. |

| 3-4  |           | Reserved                                                                                                    |

| 5-15 |           | Not used                                                                                                    |

August 15, 1984 © Copyright IBM Corporation 1984 Following is a description of the bits of the binary input register.

| Bit  | Name | Function                                                                                                                                               |

|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0-15 | Data | The current value at the<br>binary input port can be read<br>from this register. The value<br>contained is not latched<br>(unless 'BI hold' was used). |

Following is a description of the bits of the binary output register.

| Bit  | Name | Function                                                                                                                                              |

|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0-15 | Data | The value to be placed on the<br>binary output port is written<br>here. Data lines of the port<br>are affected as soon as the<br>register is written. |

#### **Binary Input Access Strategies**